- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄225499 > V58C365164S5 (MOSEL-VITELIC) 4M X 16 DDR DRAM, 0.1 ns, PDSO66 PDF資料下載

參數(shù)資料

| 型號: | V58C365164S5 |

| 廠商: | MOSEL-VITELIC |

| 元件分類: | DRAM |

| 英文描述: | 4M X 16 DDR DRAM, 0.1 ns, PDSO66 |

| 封裝: | 0.400 INCH, PLASTIC, TSOP2-66 |

| 文件頁數(shù): | 1/44頁 |

| 文件大?。?/td> | 507K |

| 代理商: | V58C365164S5 |

當前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

MOSEL VITELIC

1

V58C365164S

64 Mbit DDR SDRAM

4M X 16, 3.3VOLT

V58C365164S Rev. 1.5 November 2001

PRELIMINARY

35

4

5

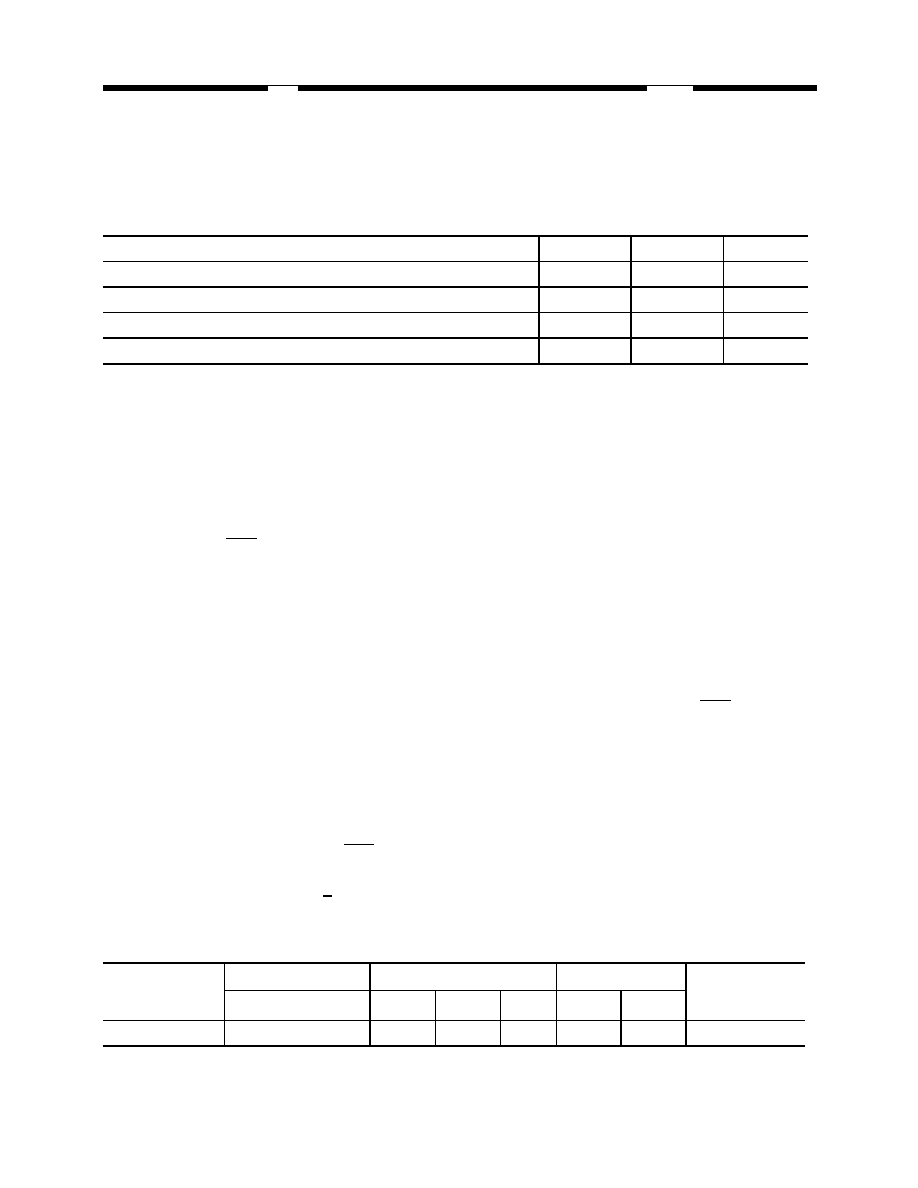

System Frequency (fCK)

275 MHz

250 MHz

200 MHz

Clock Cycle Time (tCK3)

3.5 ns

4 ns

5 ns

Clock Cycle Time (tCK2.5)

4.2 ns

4.8 ns

6 ns

Clock Cycle Time (tCK2)

5.25 ns

6 ns

7.5 ns

Features

s 4 banksx1Mbit x16 organization

s High speed data transfer rates with system

frequency up to 275 MHz

s Data Mask for Write Control (DM)

s Four Banks controlled by BA0 & BA1

s Programmable CAS Latency: 2,2.5,3

s Programmable Wrap Sequence: Sequential

or Interleave

s Programmable Burst Length:

2, 4, 8 for Sequential Type

2, 4, 8 for Interleave Type

s Automatic and Controlled Precharge Command

s Suspend Mode and Power Down Mode

s Auto Refresh and Self Refresh

s Refresh Interval: 4096 cycles/64 ms

s Available in 66-pin 400 mil TSOP-II

s SSTL-2 Compatible I/Os

s Double Data Rate (DDR)

s Bidirectional Data Strobe (DQs) for input and

output data, active on both edges

s On-Chip DLL aligns DQ and DQs transitions with

CLK transitions

s Differential clock inputs CLK and CLK

s Power supply 3.3V ± 0.3V

s VDDQ (I/O) power supply 2.5 + 0.2V

Description

The V58C365164S is a four bank DDR DRAM

organized

as

4

banks

x

1Mbit

x

16.

The

V58C365164S achieves high speed data transfer

rates by

employing

a

chip

architecture

that

prefetches multiple bits and then synchronizes the

output data to a system clock

All of the control, address, circuits are synchro-

nized with the positive edge of an externally sup-

plied clock. I/O transactions are possible on both

edges of DQS.

Operating the four memory banks in an inter-

leaved fashion allows random access operation to

occur at a higher rate than is possible with standard

DRAMs. A sequential and gapless data rate is pos-

sible depending on burst length, CAS latency and

speed grade of the device.

Device Usage Chart

Operating

Temperature

Range

Package Outline

CLK Cycle Time (ns)

Power

Temperature

Mark

JEDEC 66 TSOP II

-35

-4

-5

Std.

L

0°C to 70°C

Blank

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| V608ME06 | VCO, 1900 MHz - 2270 MHz |

| V603ME07 | VCO, 1896 MHz - 1924 MHz |

| V6049001 | VCO, 1600 MHz - 2200 MHz |

| V610ME04 | VCO, 1950 MHz - 2150 MHz |

| V62/04634-01 | SPECIALTY ANALOG CIRCUIT, PDSO14 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| V590ME01 | 制造商:ZCOMM 制造商全稱:ZCOMM 功能描述:LOW COST - HIGH PERFORMANCE VOLTAGE CONTROLLED OSCILLATOR |

| V590ME01-LF | 制造商:ZCOMM 制造商全稱:ZCOMM 功能描述:Voltage-Controlled Oscillator Surface Mount Module |

| V590ME01-LF_10 | 制造商:ZCOMM 制造商全稱:ZCOMM 功能描述:Voltage-Controlled Oscillator Surface Mount Module |

| V590ME08 | 制造商:ZCOMM 制造商全稱:ZCOMM 功能描述:VOLTAGE CONTROLLED OSCILLATOR |

| V590ME08-LF | 制造商:ZCOMM 制造商全稱:ZCOMM 功能描述:Voltage-Controlled Oscillator Surface Mount Module |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。