- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361789 > W65C134SPL-8 8-BIT MICROCONTROLLER PDF資料下載

參數(shù)資料

| 型號: | W65C134SPL-8 |

| 元件分類: | 8位微控制器 |

| 英文描述: | 8-BIT MICROCONTROLLER |

| 中文描述: | 8位微控制器 |

| 文件頁數(shù): | 9/60頁 |

| 文件大小: | 711K |

| 代理商: | W65C134SPL-8 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當(dāng)前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

WESTERN DESIGN CENTER

W65C134S

March 1, 2000

4

1.5

Chip Select Enable Register PCS3)($0007)

1.5.1

PCS is the Port 3 Chip Select Register. The PCS allows each individual chip select to be active or

non-active. When PCS30-PCS37 are equal to a "1", then CS0B to CS7B will be active. When

CS1B is active, the defined memory space for CS3B and/or CS6B is reduced. It is reduced by the

memory space 0100-011F for CS1B. When CS2B is active, the defined memory space for CS3B

and/or CS6B is reduced. It is reduced by the memory space 0120-013F for CS2B.

CS7B is automatically enabled when BCR7=1.

The W65C134S will use the internal RAM as stack when PCS33 and PCS36 are disabled. If PCS33

or PCS36 are enabled then the off chip stack is used.

1.5.2

1.5.3

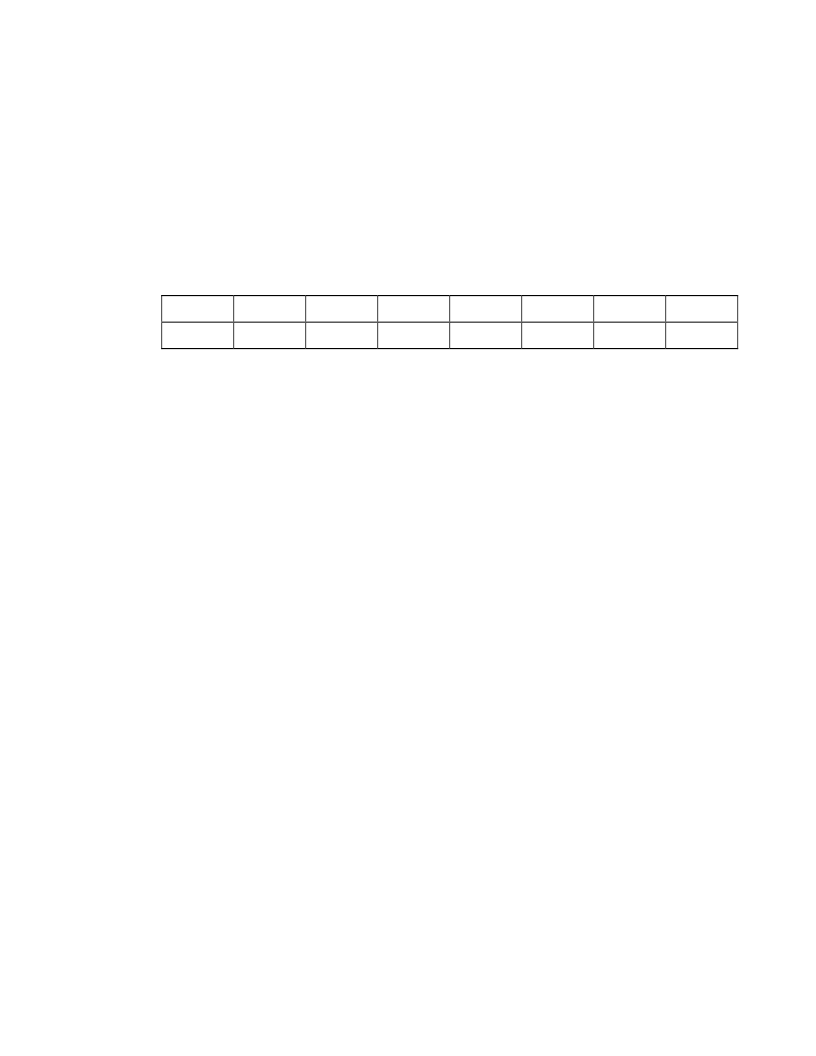

7

6

5

4

3

2

1

0

CS7B

CS6B

CS5B

CS4B

CS3B

CS2B

CS1B

CS0B

Figure 1-3 Chip Select Enable Register

1.6

The Timers

1.6.1

1.6.2

Upon Timer clock input negative edge the timer low counter is decremented by 1.

When T1 or T2 prescaler mode is enabled, (making timer low counter a divide-by-N+1 prescaler)

then timer low counter is reloaded from timer low latch. Monitor Timer M does not have a prescaler

mode.

A write to the timer low counter writes the timer low latch.

A read of the timer high or low counter reads the timer high or low counter.

Upon Timer clock input negative edge when the timer low counter reaches zero, the timer high

counter is decremented by 1. Upon Timer clock input positive edge, when the timer high counter

reaches zero, this sequence occurs:

1.6.5.1

Timer 1 and 2 set their associated interrupt flag. If the interrupt is enabled the MPU is

then interrupted and control is transferred to the vector associated with the interrupt.

When Timer M times out, the W65C134S is restarted: on-chip logic pulls RESB pin

low for 2 CLK cycles and releases RESB to go high, "restarting" the W65C134S.

1.6.5.2

The timer hi counter is loaded from the timer hi latch, and timer low counter is loaded

from timer low latch.

A write to the Timer 1, 2 or A high counter writes to the timer hi latch and this sequence occurs:

1.6.6.1

The timer hi latch is loaded from data bus.

1.6.6.2

The timer low counter is loaded from the timer low latch, and the timer hi counter is

loaded from the timer hi latch.

Timer M is disabled after RESB and is activated by the first Timer Control Register One (TCR10)

transition from "0" to "1" (the first load of Timer M).

1.6.7.1

The Timer M counter is reloaded with the value in the Timer M latches when the TCR10

bit 0 makes a transition from a "0" to "1". TCR10 transition from a "1" to a "0" has no

effect on the timer.

1.6.3

1.6.4

1.6.5

1.6.6

1.6.7

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| W65C134SQ-8 | 8-BIT MICROCONTROLLER |

| W65C29P-6 | I/O Controller |

| W65C29P-8 | I/O Controller |

| W65C22S8P-8 | Peripheral Interface |

| W65C22S8PL-8 | Peripheral Interface |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| W65C134SQ-8 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| W65C21N6TPG-14 | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI Peripheral Interface Adapter RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| W65C21N6TPLG-14 | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI Peripheral Interface Adapter RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| W65C21S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Peripheral Interface Adapter (PIA) |

| W65C21S6TPG-14 | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI Peripheral Interface Adapter RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。