- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376455 > XR17D158IV (EXAR CORP) UNIVERSAL (3.3V AND 5V) PCI BUS OCTAL UART PDF資料下載

參數(shù)資料

| 型號(hào): | XR17D158IV |

| 廠商: | EXAR CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | UNIVERSAL (3.3V AND 5V) PCI BUS OCTAL UART |

| 中文描述: | 8 CHANNEL(S), 6.25M bps, SERIAL COMM CONTROLLER, PQFP144 |

| 封裝: | 20 X 20 MM, 1.40 MM HEIGHT, TQFP-144 |

| 文件頁(yè)數(shù): | 33/72頁(yè) |

| 文件大小: | 1520K |

| 代理商: | XR17D158IV |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)當(dāng)前第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)

xr

REV. 1.2.1

UNIVERSAL (3.3V AND 5V) PCI BUS OCTAL UART

XR17D158

33

5.3.3

Receiver Operation with FIFO

5.4

Automatic hardware RTS/CTS or DTR/DSR flow control is used to prevent data overrun to the local receiver

FIFO and remote receiver FIFO. The RTS#/DTR# output pin is used to request the remote unit to suspend/

restart data transmission while the CTS#/DSR# input pin is monitored to suspend/restart the local transmitter.

The auto RTS/CTS or DTR/DSR flow control features are individually selected to fit specific application

requirement and enabled through EFR bit-6 and 7 and MCR bit-2 for either RTS/CTS or DTR/DSR control

signals.

Automatic Hardware (RTS/CTS or DTR/DSR) Flow Control Operation

Auto RTS flow control must be started by asserting the RTS# output pin LOW (MCR bit-1 = 1). Similarly, Auto

DTR flow control must be started by asserting the DTR# output pin LOW (MCR bit-0 = 1).

Figure 16

shows in

detail how automatic hardware flow control works.

F

IGURE

15. R

ECEIVER

O

PERATION

IN

FIFO

AND

F

LOW

C

ONTROL

M

ODE

T

ABLE

11: A

UTO

RTS/CTS

OR

DTR/DSR F

LOW

C

ONTROL

S

ELECTION

MCR B

IT

-2

EFR B

IT

-7

EFR B

IT

-6

H

ARDWARE

F

LOW

C

ONTROL

S

ELECTION

0

1

X

Auto CTS Flow Control Enabled

0

X

1

Auto RTS Flow Control Enabled

1

1

X

Auto DSR Flow Control Enabled

1

X

1

Auto DTR Flow Control Enabled

X

0

0

No Hardware Flow Control

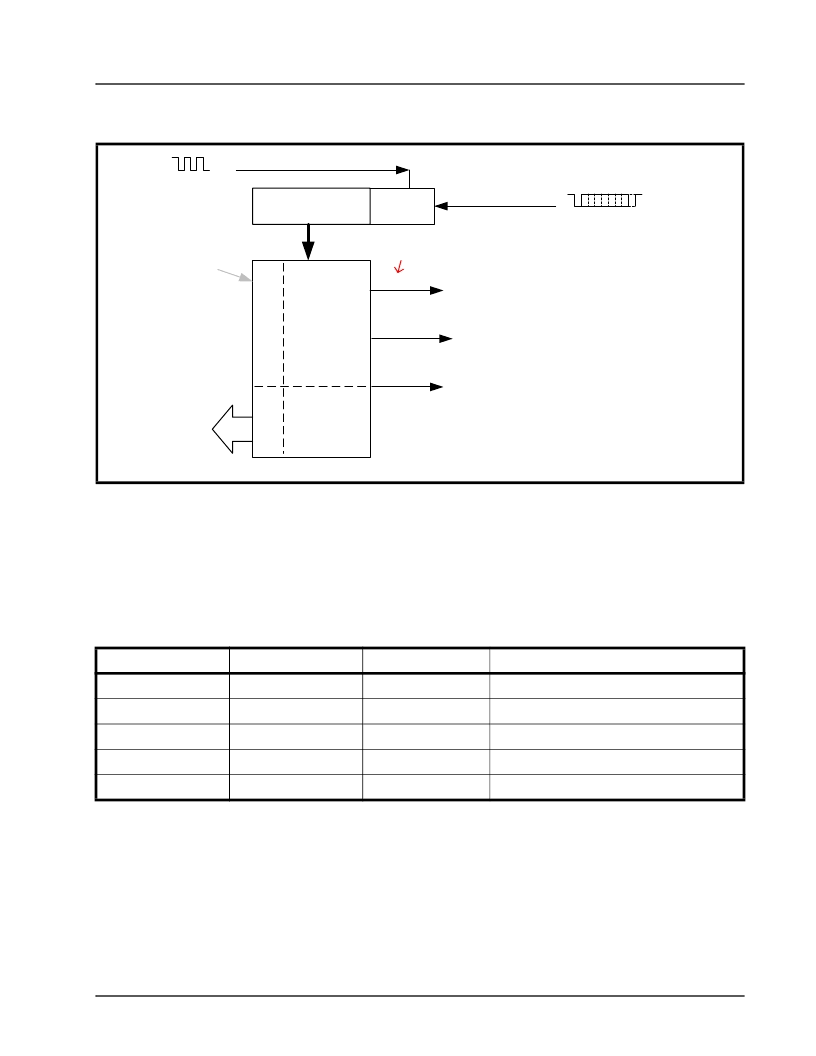

Receive Data Shift

Register (RSR)

RXFIFO1

16X or 8X Sampling

Clock (8XMODE Reg.)

E

(

E

L

64 bytes by 11-

bit wide FIFO

Receive Data Characters

FIFO Trigger=48

Example:

- FIFO trigger level set at 48 bytes

- RTS/DTR hyasteresis set at +/-8 chars.

Data fills to 56

Data falls to 40

Data Bit

Validation

Receive Data

FIFO

(64-byte)

Receive

Data

Receive Data

Byte and Errors

RHR Interrupt (ISR bit-2) is programmed

at FIFO trigger level (RXTRG).

FIFO is Enable by FCR bit-0=1

RTS#/DTR# de-asserts when data fills above

the trigger level to suspend remote transmitter.

Enable by EFR bit-6=1, MCR bit-2.

RTS#/DTR# re-asserts when data falls below

the trigger level to restart remote transmitter.

Enable by EFR bit-6=1, MCR bit-2.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XR17D158 | UNIVERSAL (3.3V AND 5V) PCI BUS OCTAL UART |

| XR17D158CV | UNIVERSAL (3.3V AND 5V) PCI BUS OCTAL UART |

| XR17L152IM | CAP .068UF 400V PEN FILM 2825 5% |

| XR17L152 | 3.3V PCI BUS DUAL UART |

| XR17L152CM | 3.3V PCI BUS DUAL UART |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR17D158IV-F | 功能描述:UART 接口集成電路 3.3V-5V 64B FIFO temp -45 to 85C;UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR17D158IVTR-F | 制造商:Exar Corporation 功能描述:UART 8-CH 64Byte FIFO 5V 144-Pin LQFP T/R 制造商:Exar Corporation 功能描述:XR17D158IVTR-F |

| XR17L152 | 制造商:EXAR 制造商全稱:EXAR 功能描述:3.3V PCI BUS DUAL UART |

| XR17L152CM | 制造商:EXAR 制造商全稱:EXAR 功能描述:3.3V PCI BUS DUAL UART |

| XR17L152IM | 制造商:EXAR 制造商全稱:EXAR 功能描述:3.3V PCI BUS DUAL UART |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。