- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376455 > XR17D158IV (EXAR CORP) UNIVERSAL (3.3V AND 5V) PCI BUS OCTAL UART PDF資料下載

參數(shù)資料

| 型號(hào): | XR17D158IV |

| 廠商: | EXAR CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | UNIVERSAL (3.3V AND 5V) PCI BUS OCTAL UART |

| 中文描述: | 8 CHANNEL(S), 6.25M bps, SERIAL COMM CONTROLLER, PQFP144 |

| 封裝: | 20 X 20 MM, 1.40 MM HEIGHT, TQFP-144 |

| 文件頁(yè)數(shù): | 69/72頁(yè) |

| 文件大小: | 1520K |

| 代理商: | XR17D158IV |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)當(dāng)前第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)

xr

REV. 1.2.1

UNIVERSAL (3.3V AND 5V) PCI BUS OCTAL UART

XR17D158

69

NOTICE

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to

improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any

circuits described herein, conveys no license under any patent or other right, and makes no representation that

the circuits are free of patent infringement. Charts and schedules contained here in are only for illustration

purposes and may vary depending upon a user’s specific application. While the information in this publication

has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the

failure or malfunction of the product can reasonably be expected to cause failure of the life support system or

to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless

EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has

been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately

protected under the circumstances.

Copyright 2004 EXAR Corporation

Datasheet November 2004.

Send your UART technical inquiry with technical details to hotline:

uarttechsupport@exar.com

.

Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.

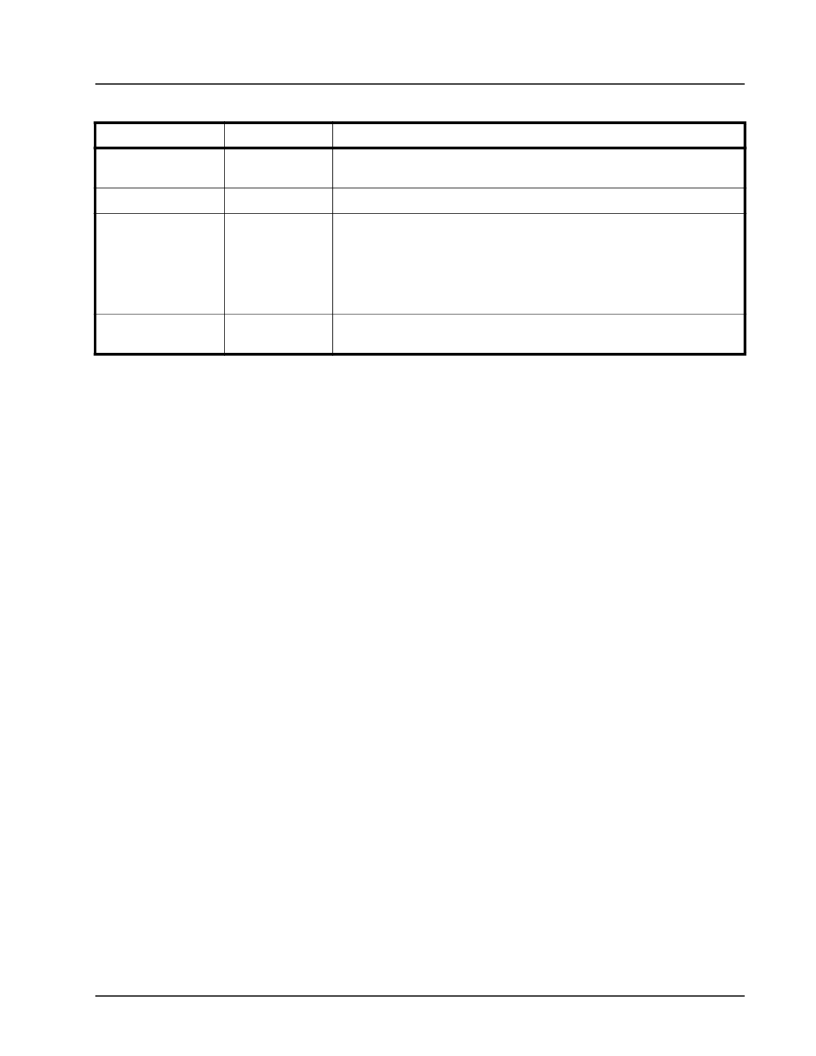

REVISION HISTORY

D

ATE

R

EVISION

D

ESCRIPTION

May 2003

1.0.0

Final Production Release. Updated AC and DC specifications. Clarified PCI

Burst Read and Write Transactions.

July 2003

1.1.0

Added Device Status to Ordering Information.

June 2004

1.2.0

Clarified pin descriptions- changed from using logic 1 and logic 0 to HIGH

(VCC) and LOW (GND) for input and output pin descriptions. Clarified Auto

RS485 and Sleep Mode description. Added timing diagram for external

clock input at XTAL1 pin (

Figure 19

) and T

ECLK

, T

ECH

, and T

ECL

to AC Elec-

trical Specifications. The Device Revision Register (DREV) has been

updated to 0x03 for devices with top mark date code "C2 YYWW".

November 2004

1.2.1

The Device Revision Register (DREV) has been updated to 0x09 for devices

with top mark date code "I2 YYWW".

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XR17D158 | UNIVERSAL (3.3V AND 5V) PCI BUS OCTAL UART |

| XR17D158CV | UNIVERSAL (3.3V AND 5V) PCI BUS OCTAL UART |

| XR17L152IM | CAP .068UF 400V PEN FILM 2825 5% |

| XR17L152 | 3.3V PCI BUS DUAL UART |

| XR17L152CM | 3.3V PCI BUS DUAL UART |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR17D158IV-F | 功能描述:UART 接口集成電路 3.3V-5V 64B FIFO temp -45 to 85C;UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR17D158IVTR-F | 制造商:Exar Corporation 功能描述:UART 8-CH 64Byte FIFO 5V 144-Pin LQFP T/R 制造商:Exar Corporation 功能描述:XR17D158IVTR-F |

| XR17L152 | 制造商:EXAR 制造商全稱:EXAR 功能描述:3.3V PCI BUS DUAL UART |

| XR17L152CM | 制造商:EXAR 制造商全稱:EXAR 功能描述:3.3V PCI BUS DUAL UART |

| XR17L152IM | 制造商:EXAR 制造商全稱:EXAR 功能描述:3.3V PCI BUS DUAL UART |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。