- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376455 > XR17L152 (Exar Corporation) 3.3V PCI BUS DUAL UART PDF資料下載

參數(shù)資料

| 型號(hào): | XR17L152 |

| 廠商: | Exar Corporation |

| 英文描述: | 3.3V PCI BUS DUAL UART |

| 中文描述: | 3.3V的PCI總線雙UART |

| 文件頁(yè)數(shù): | 28/55頁(yè) |

| 文件大小: | 318K |

| 代理商: | XR17L152 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)當(dāng)前第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)

á

DISCONTINUED

XR17L152

3.3V PCI BUS DUAL UART

REV. 1.1.0

28

N

OTE

:

MCR bits 2 and 3 (OP1 and OP2 outputs) are not available in the XR17L154. They are present for 16C550

compatibility during Internal loopback, see

Figure 11

.

4.6

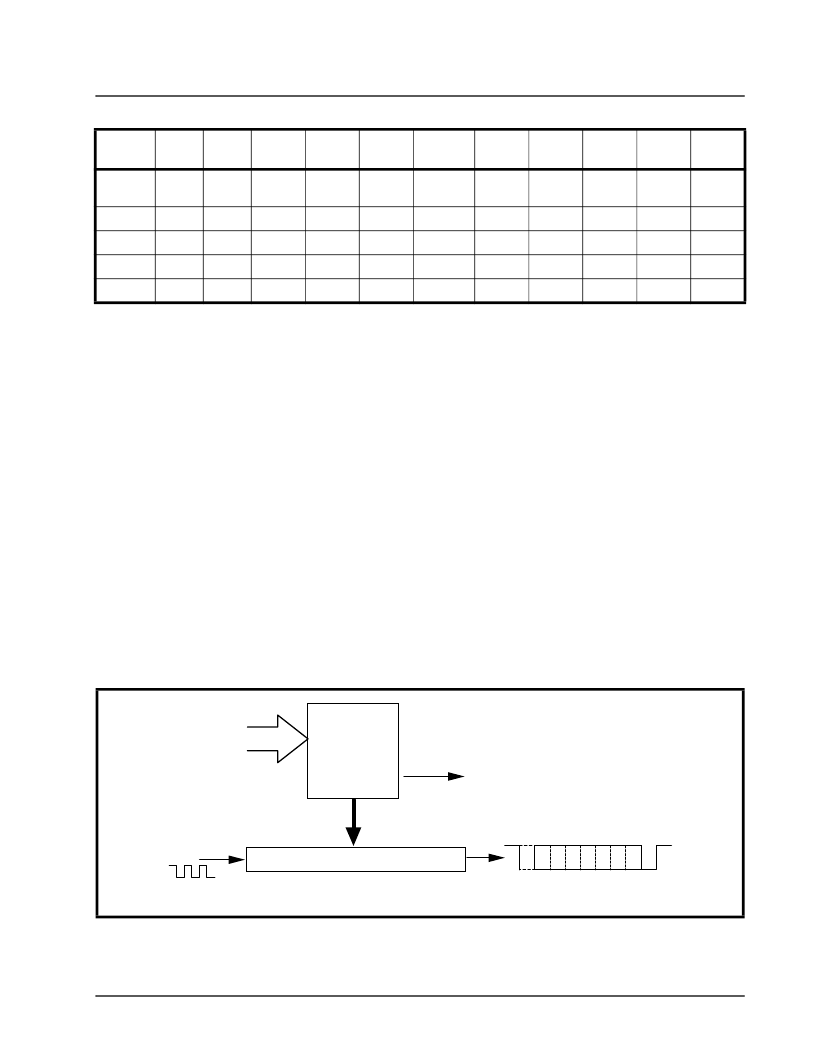

Transmitter

The transmitter section comprises of 64 bytes of FIFO, a byte-wide Transmit Holding Register (THR) and an 8-

bit Transmit Shift Register (TSR). THR receives a data byte from the host (non-FIFO mode) or a data byte from

the FIFO

when the FIFO is enabled by FCR bit-0. TSR shifts out every data bit with the 16X or 8X internal

clock. A bit time is 16 or 8 clock periods. The transmitter sends the start bit followed by the number of data bits,

inserts the proper parity bit if enable, and adds the stop bit(s). The status of the THR and TSR are reported in

the Line Status Register (LSR bit-5 and bit-6).

4.6.1

Transmit Holding Register (THR)

The Transmit Holding Register is an 8-bit register providing a data interface to the host processor. The host

writes transmit data byte to the THR to be converted into a serial data stream including start-bit, data bits,

parity-bit and stop-bit(s). The least-significant-bit (Bit-0) becomes first data bit to go out. The THR is also the

input register to the transmit FIFO of 64 bytes when FIFO operation is enabled by FCR bit-0. A THR empty

interrupt can be generated when it is enabled in IER bit-1.

4.6.2

Transmitter Operation in non-FIFO

The host loads transmit data to THR one character at a time. The THR empty flag (LSR bit-5) is set when the

data byte is transferred to TSR. THR flag can generate a transmit empty interrupt (ISR bit-1) when it is enabled

by IER bit-1. The TSR flag (LSR bit-6) is set when TSR becomes completely empty.

1 1 0 0

XCHAR

R

Xon Det.

Indicator

Xoff Det.

Indicator

Self-clear

after read

1 1 0 0

XOFF1

W

Bit-7

Bit-6

Bit-5

Bit-4

Bit-3

Bit-2

Bit-1

Bit-0

1 1 0 1

XOFF2

W

Bit-7

Bit-6

Bit-5

Bit-4

Bit-3

Bit-2

Bit-1

Bit-0

1 1 1 0

XON1

W

Bit-7

Bit-6

Bit-5

Bit-4

Bit-3

Bit-2

Bit-1

Bit-0

1 1 1 1

XON2

W

Bit-7

Bit-6

Bit-5

Bit-4

Bit-3

Bit-2

Bit-1

Bit-0

F

IGURE

12. T

RANSMITTER

O

PERATION

IN

NON

-FIFO M

ODE

T

ABLE

11: UART CHANNEL CONFIGURATION REGISTERS DESCRIPTION.

S

HADED

BITS

ARE

ENABLED

BY

EFR B

IT

-4.

A

DDRESS

A3-A0

R

EG

N

AME

R

EAD

/

W

RITE

B

IT

-7

B

IT

-6

B

IT

-5

B

IT

-4

B

IT

-3

B

IT

-2

B

IT

-1

B

IT

-0

C

OMMENT

Transmit

Holding

Register

(THR)

Transmit Shift Register (TSR)

Data

Byte

L

S

B

M

S

B

THR Interrupt (ISR bit-1)

Enabled by IER bit-1

TXNOFIFO1

16X or 8X

Clock

(8XMODE

Register)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XR17L152CM | 3.3V PCI BUS DUAL UART |

| XR2001 | High-Voltage, High-Current Darlington Transistor Arrays |

| XR2002CN | High-Voltage, High-Current Darlington Transistor Arrays |

| XR2003 | High-Voltage, High-Current Darlington Transistor Arrays |

| XR2003CN | Programable Driver IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR17L152CM | 制造商:EXAR 制造商全稱:EXAR 功能描述:3.3V PCI BUS DUAL UART |

| XR17L152IM | 制造商:EXAR 制造商全稱:EXAR 功能描述:3.3V PCI BUS DUAL UART |

| XR17L154 | 制造商:EXAR 制造商全稱:EXAR 功能描述:3.3V PCI BUS QUAD UART |

| XR17L154CV | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecomm/Datacomm |

| XR17L154IV | 制造商:EXAR 制造商全稱:EXAR 功能描述:3.3V PCI BUS QUAD UART |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。