- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376462 > XRT75L00D (Exar Corporation) E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER PDF資料下載

參數(shù)資料

| 型號(hào): | XRT75L00D |

| 廠商: | Exar Corporation |

| 英文描述: | E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER |

| 中文描述: | E3/DS3/STS-1線路接口單元與SONET DESYNCHRONIZER |

| 文件頁(yè)數(shù): | 43/92頁(yè) |

| 文件大?。?/td> | 894K |

| 代理商: | XRT75L00D |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)當(dāng)前第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)

XRT75L00D

REV. 1.0.2

E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER

38

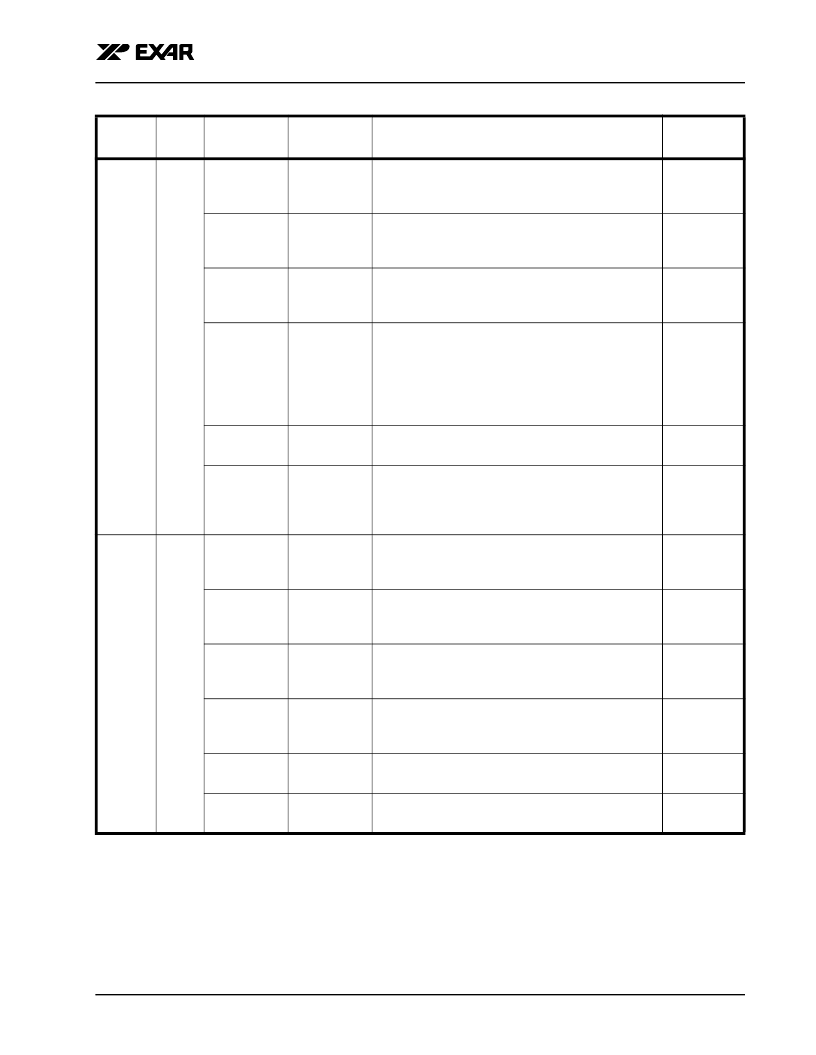

0x01

R/W

D0

DMOIE

Writing a “1” to this bit field enables the DMO inter-

rupt and triggers an interrupt when the transmitter

driver fails. Writing a “0” disables the interrupt.

0

D1

RLOSIE

Writing a “1” to this bit field enables the RLOS inter-

rupt and triggers an interrupt when the RLOS condi-

tion occurs. Writing a “0” disables the interrupt.

0

D2

RLOLIE

Writing a “1” to this bit field enables the RLOL inter-

rupt and triggers an interrupt when RLOL condition

occurs. Writing a “0” disables the interrupt.

0

D3

FLIE

Writing a “1” to this bit field enables the FL interrupt

and triggers an interrupt when the FIFO Limit of the

Jitter Attenuator is within 2 bits of overflow/underflow

condition. Writing a “0” disables the interrupt.

N

OTE

:

This bit field is ignored when the Jitter

Attenuator is disabled.

0

D4

PRBSIE

Writing a “1” to this bit enables the PRBS bit error

interrupt.

0

D5

CNT_SATIE

Writing a “1” to this bit enables the PRBS error-

counter saturation interrupt. When the PRBS error

counter reaches 0xFFFF, an interrupt will be gener-

ated.

0

0x02

Reset

Upon

Read

D0

DMOIS

This bit is set to “1” every time a DMO status change

has occurred since the last cleared interrupt.This bit

is cleared when read.

0

D1

RLOSIS

This bit is set to “1” every time a RLOS status change

has occurred since the last cleared interrupt. This bit

is cleared when read.

0

D2

RLOLIS

This bit is set to “1” every time a RLOL status change

has occurred since the last cleared interrupt. This bit

is cleared when read.

0

D3

FLIS

This bit is set to “1” every time a FIFO Limit status

change has occurred since the last cleared interrupt.

This bit is cleared when read.

0

D4

PRBSIS

This bit is set to “1” when a PRBS bit error is

detected. This bit is cleared when read.

0

D5

CNT_SATIS

This bit is set to “1” when the PRBS error counter has

saturated (0xFFFF). This bit is cleared when read.

0

T

ABLE

16: R

EGISTER

M

AP

D

ESCRIPTION

A

DDRESS

(H

EX

)

T

YPE

B

IT

L

OCATION

S

YMBOL

D

ESCRIPTION

D

EFAULT

V

ALUE

(B

IN

)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT75L00DIV | E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER |

| XRT75L02 | TWO CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER |

| XRT75L02IV | TWO CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER |

| XRT75L03D | THREE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER |

| XRT75L04D | FOUR CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT75L00DES | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 LIU+DESYNCH 3.3V LIU+DESYNCH 3.3V RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| XRT75L00DIV | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI 3.3V 1 CH E3/DS3/STS W/SONET DE-SYNCH RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| XRT75L00DIV-F | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI 1-Ch DS3, E3, SONET RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| XRT75L00DIVTR | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 3.3V 1 CH E3/DS3/STS W/SONET DE-SYNCH RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| XRT75L00DIVTR-F | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 3.3V 1 CH E3/DS3/STS W/SONET DE-SYNCH RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。