- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376462 > XRT75L03D (Exar Corporation) THREE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER PDF資料下載

參數(shù)資料

| 型號(hào): | XRT75L03D |

| 廠商: | Exar Corporation |

| 英文描述: | THREE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER |

| 中文描述: | Three頻道E3/DS3/STS-1線路接口單元與SONET DESYNCHRONIZER |

| 文件頁(yè)數(shù): | 111/134頁(yè) |

| 文件大?。?/td> | 659K |

| 代理商: | XRT75L03D |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)當(dāng)前第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)

á

THREE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER

XRT75L03D

REV. 1.0.0

106

In the "Slip Buffer, the "input" STS-1 data (labeled "STS-1 Data_IN") is latched into the FIFO, upon a given

edge of the corresponding "STS-1 Clock_f1" input clock signal. The STS-1 Data (labeled "STS-1 Data_OUT")

is clocked out of the Slip Buffer upon a given edge of the "STS-1 Clock_f2" input clock signal.

The behavior of the data, passing through the "Slip Buffer" is now described for each possible relationship

between frequencies f1 and f2.

If f1 = f2

If both frequencies, f1 and f2 are exactly equal, then the STS-1 data will be "clocked" into the "Slip Buffer" at

exactly the same rate that it is "clocked out". In this case, the "Slip Buffer" will neither fill-up nor become

depleted. As a consequence, no pointer-adjustments will occur in this STS-1 data stream. In other words, the

STS-1 SPE will remain at a constant location (or offset) within each STS-1 envelope capacity for the duration

that this STS-1 signal is supporting this particular service.

If f1 < f2

If frequency f1 is less than f2, then this means that the STS-1 data is being "clocked out" of the "Slip Buffer" at

a faster rate than it is being clocked in. In this case, the "Slip Buffer" will eventually become depleted.

Whenever this occurs, a typical strategy is to "stuff" (or insert) a "dummy byte" into the data stream. The

purpose of stuffing this "dummy byte" is to compensate for the frequency differences between f1 and f2, and

attempt to keep the "Slip Buffer, at a somewhat constant fill level.

N

OTE

:

This "dummy byte" does not carry any valuable information (not for the user, nor for the system).

Since this "dummy byte" carries no useful information, it is important that the "Receiving PTE" be notified

anytime this "dummy byte" stuffing occurs. This way, the Receiving Terminal can "know" not to treat this

"dummy byte" as user data.

Byte-Stuffing and Pointer Incrementing in a SONET Network

Whenever this "byte-stuffing" occurs then the following other things occur within the STS-1 data stream.

During the STS-1 frame that contains the "Byte-Stuffing" event

a.

The "stuff-byte" will be inserted into the byte position immediately after the H3 byte. This insertion of the

"dummy byte" immediately after the H3 byte position will cause the J1 byte (and in-turn, the rest of the

SPE) to be "byte-shifted" away from the H3 byte. As a consequence, the offset between the H3 byte posi-

tion and the STS-1 SPE will now have been increased by 1 byte.

b.

The "Transmitting" Network Equipment will notify the remote terminal of this byte-stuffing event, by invert-

ing certain bits within the "pointer word" (within the H1 and H2 bytes) that are referred to as "I" bits.

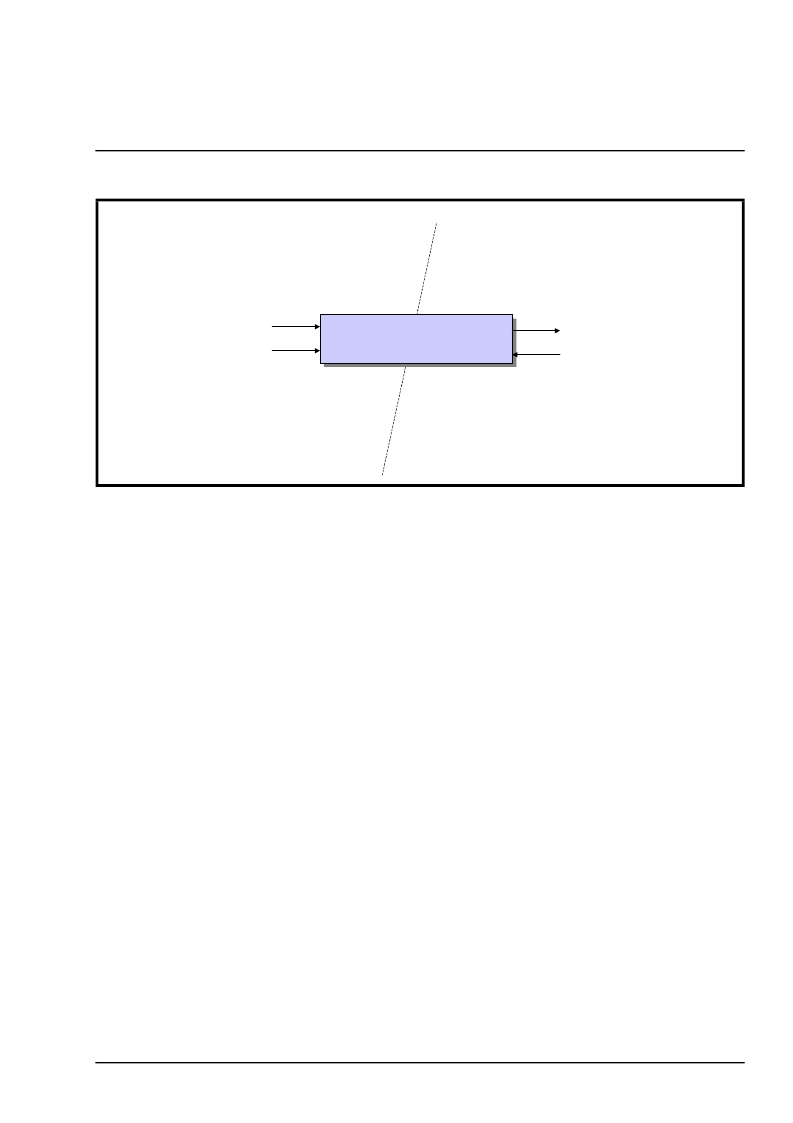

F

IGURE

44. A

N

I

LLUSTRATION

OF

AN

STS-1

SIGNAL

BEING

PROCESSED

VIA

A

S

LIP

B

UFFER

SLIP BUFFER

STS-1 Data_IN

STS-1 Clock_f1

STS-1 Data_OUT

STS-1 Clock_f2

Clock Domain operating

At frequency f1

Clock Domain operating

At Frequency f2.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT75L04D | FOUR CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER |

| XRT75L04DIV | FOUR CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER |

| XRT75L04 | FOUR CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER |

| XRT75L04IV | FOUR CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER |

| XRT75L06D | SIX CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT75L03DES | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 3 CH T3/E3/STS1 LIU+DESYNCH3.3V RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| XRT75L03DIV | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI 3CHNNEL E3/DS3/STS 1 SONET DE-SYNCH RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| XRT75L03DIV-F | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI 3-Ch DS3, E3, STS-1 RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| XRT75L03DIVTR | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 3CHNNEL E3/DS3/STS 1 SONET DE-SYNCH RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| XRT75L03DIVTR-F | 功能描述:接口 - 專用 RoHS:否 制造商:Texas Instruments 產(chǎn)品類型:1080p60 Image Sensor Receiver 工作電源電壓:1.8 V 電源電流:89 mA 最大功率耗散: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:BGA-59 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。