- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376462 > XRT75R03DIV (EXAR CORP) THREE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCRONIZER PDF資料下載

參數(shù)資料

| 型號: | XRT75R03DIV |

| 廠商: | EXAR CORP |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | THREE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCRONIZER |

| 中文描述: | DATACOM, PCM TRANSCEIVER, PQFP128 |

| 封裝: | 14 X 20 MM, LQFP-128 |

| 文件頁數(shù): | 54/134頁 |

| 文件大小: | 803K |

| 代理商: | XRT75R03DIV |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁當前第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁

XRT75R03D

REV. 1.0.2

THREE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCRONIZER

49

6.4.3

When the LOS condition is declared, the clock recovery circuit locks into the reference clock applied to the

ExClk_n pin and output this clock on the RxClk_n output.In Single Frequency Mode (SFM), the clock recovery

locks into the rate clock generated and output this clock on the RxClk_n pins. The data on the RPOS_n and

RNEG_n pins can be forced to zero by pulling the LOSMUT pin “High” (in Hardware Mode) or by setting the

LOSMUT_n bits in the individual channel control register to “1” (in Host Mode).

Muting the Recovered Data with LOS condition:

N

OTE

:

When the LOS condition is cleared, the recovered data is output on RPOS_n and RNEG_n pins.

7.0

There are three fundamental parameters that describe circuit performance relative to jitter:

Jitter Tolerance (Receiver)

Jitter Transfer (Receiver/Transmitter)

Jitter Generation

7.1

J

ITTER

T

OLERANCE

- R

ECEIVER

:

Jitter tolerance is a measure of how well a Clock and Data Recovery unit can successfully recover data in the

presence of various forms of jitter. It is characterized by the amount of jitter required to produce a specified bit

error rate. The tolerance depends on the frequency content of the jitter. Jitter Tolerance is measured as the

jitter amplitude over a jitter spectrum for which the clock and data recovery unit achieves a specified bit error

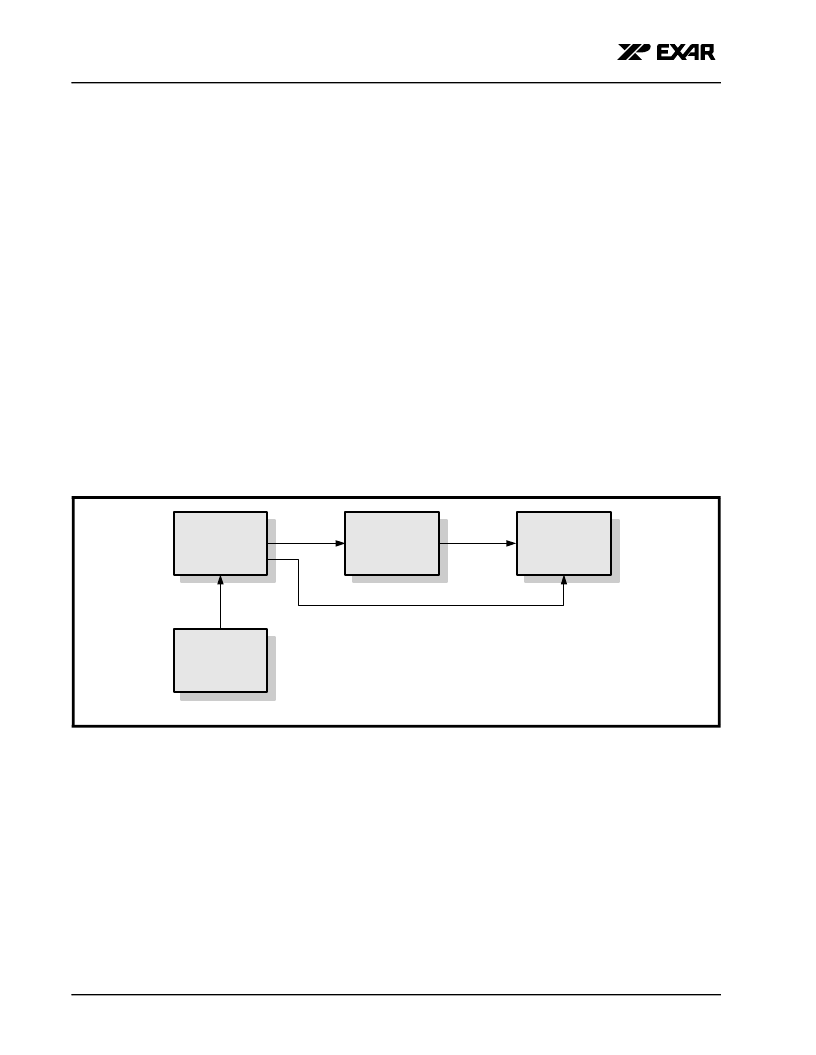

rate (BER). To measure the jitter tolerance as shown in Figure 21, jitter is introduced by the sinusoidal

modulation of the serial data bit sequence.

JITTER:

Input jitter tolerance requirements are specified in terms of compliance with jitter mask which is represented as

a combination of points.Each point corresponds to a minimum amplitude of sinusoidal jitter at a given jitter

frequency.

7.1.1

DS3/STS-1 Jitter Tolerance Requirements:

Bellcore GR-499 CORE, Issue 1, December 1995 specifies the minimum requirement of jitter tolerance for

Category I and Category II. The jitter tolerance requirement for Category II is the most stringent. Figure 22

shows the jitter tolerance curve as per GR-499 specification.

F

IGURE

22. J

ITTER

T

OLERANCE

M

EASUREMENTS

FREQ

Synthesizer

Pattern

Generator

DUT

XRT75VL03D

Error

Detector

Modulation

Freq.

Data

Clock

相關PDF資料 |

PDF描述 |

|---|---|

| XRT75R03 | THREE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

| XRT75R03IV | THREE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

| XRT75R06D | SIX CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER |

| XRT75R06DIB | SIX CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER |

| XRT75R06 | SIX CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| XRT75R03DIV-F | 功能描述:網(wǎng)絡控制器與處理器 IC 3-Ch E3/DS3/STS-1 RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| XRT75R03DIVTR | 功能描述:時鐘合成器/抖動清除器 3CHNNEL E3/DS3/STS 1 JITTER ATTENUATOR RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| XRT75R03DIVTR-F | 功能描述:接口 - 專用 RoHS:否 制造商:Texas Instruments 產(chǎn)品類型:1080p60 Image Sensor Receiver 工作電源電壓:1.8 V 電源電流:89 mA 最大功率耗散: 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:BGA-59 |

| XRT75R03ES | 功能描述:時鐘合成器/抖動清除器 3CH T3/E3/STS1LIU+JA 3.3V W/REDUNDANCY RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| XRT75R03IV | 功能描述:外圍驅動器與原件 - PCI 3CHNNEL E3/DS3/STS 1 JITTER ATTENUATOR RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復。