- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366309 > a8251 (Altera Corporation) Programmable Communications Interface(可編程通信接口) PDF資料下載

參數(shù)資料

| 型號(hào): | a8251 |

| 廠商: | Altera Corporation |

| 英文描述: | Programmable Communications Interface(可編程通信接口) |

| 中文描述: | 可編程通信接口(可編程通信接口) |

| 文件頁數(shù): | 12/21頁 |

| 文件大小: | 338K |

| 代理商: | A8251 |

36

Altera Corporation

a8251 Programmable Communications Interface Data Sheet

For example, after detecting a logic low in divide-by-1 mode, the

a8251

assumes data is available on the next rising edge. However, after

detecting a logic low in divide-by-16 mode, the

a8251

counts 8

nrxc

edges and samples again. The data must still be a logic low. At this point,

the

a8251

assumes the data and clock are synchronized, and samples

data every 16 clock edges thereafter. Divide-by-64 mode is similar to

divide-by-16, with the start bit sampled at the first rising edge and the

32nd rising edge of

nrxc

. Data is then sampled every 64 rising edges.

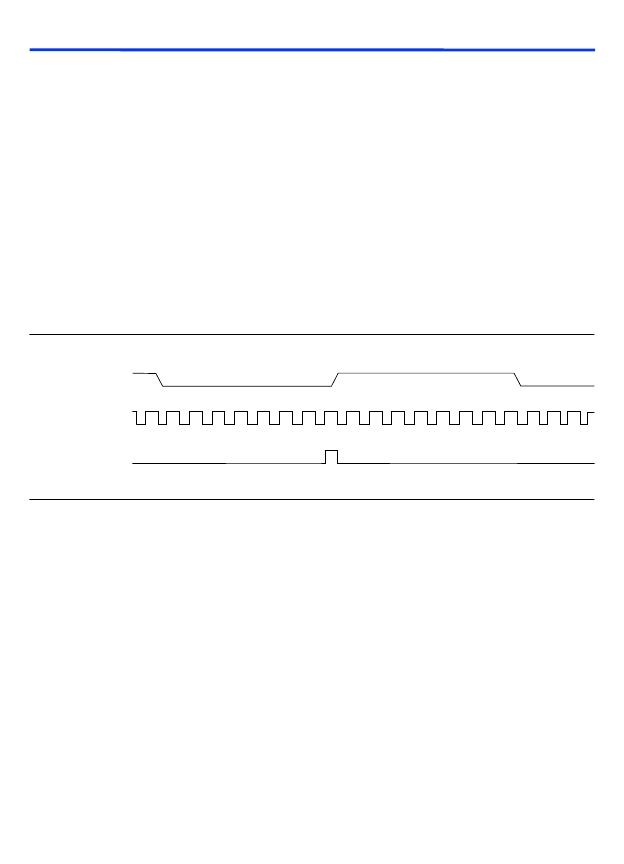

Data Bit Sampling

After detecting a start bit, the

a8251

samples and shifts the data into the

shift register. Data bit sampling occurs on every rising edge in divide-by-

1 mode, every 16 rising edges in divide-by-16 mode, and every 64 rising

edges in divide-by-64 mode. Each time a bit is sampled, parity is

calculated for future error detection. See

Figure 3

.

Figure 3. Receiver Clock Signals

Parity/Stop Bit Detection

The

a8251

counts the number of data bits as it shifts. When the number

of data bits received matches the number specified in the control register,

the

a8251

expects either a parity bit or a stop bit.

If parity is enabled, the

a8251

samples for the parity bit, which is

processed for parity but is not shifted into the shift register. After the

parity bit, or after the last data bit if parity is not enabled, the

a8251

expects a stop bit (i.e., logic high). If a logic low is sampled, the

fe

bit is

set in the status register.

The

a8251

receives data with one or two stop bits. If one stop bit is

specified in the control register, the

a8251

will expect one stop bit before

starting the synchronization process. Similarly, if two stop bits are

specified, the synchronization process begins after detecting two logic

highs.

nrxc (Divide-by-1)

nrxc (Divide-by-16)

Sampling Pulse

(Divide-by-16)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| a8255 | Programmable Peripheral Interface Adapter(可編程外圍接口適配器) |

| A8255 | PROGRAMMABLE PERIPHERAL INTERFACE ADAPTER |

| a8259 | Programmable Interrupt Controller(可編程中斷控制器) |

| A8406-53 | Various types of cables for frame grabber |

| A8406-54 | Various types of cables for frame grabber |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A825100-4 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| A8255 | 制造商:ALTERA 制造商全稱:Altera Corporation 功能描述:PROGRAMMABLE PERIPHERAL INTERFACE ADAPTER |

| A82564000AP | 制造商:Panasonic Industrial Company 功能描述:LEVER |

| A82564210AP | 制造商:Panasonic Industrial Company 功能描述:LEVER |

| A82565540AP | 制造商:Panasonic Industrial Company 功能描述:LEVER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。