- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄8579 > AD9776BSVZRL (Analog Devices Inc)IC DAC 12BIT DUAL 1GSPS 100TQFP PDF資料下載

參數(shù)資料

| 型號: | AD9776BSVZRL |

| 廠商: | Analog Devices Inc |

| 文件頁數(shù): | 21/56頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC DAC 12BIT DUAL 1GSPS 100TQFP |

| 產(chǎn)品培訓(xùn)模塊: | DAC Architectures |

| 標(biāo)準(zhǔn)包裝: | 1,000 |

| 位數(shù): | 12 |

| 數(shù)據(jù)接口: | 并聯(lián) |

| 轉(zhuǎn)換器數(shù)目: | 2 |

| 電壓電源: | 模擬和數(shù)字 |

| 功率耗散(最大): | 300mW |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 100-TQFP 裸露焊盤 |

| 供應(yīng)商設(shè)備封裝: | 100-TQFP-EP(14x14) |

| 包裝: | 帶卷 (TR) |

| 輸出數(shù)目和類型: | 4 電流,單極 |

| 采樣率(每秒): | 1G |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當(dāng)前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁

AD9776/AD9778/AD9779

Rev. A | Page 28 of 56

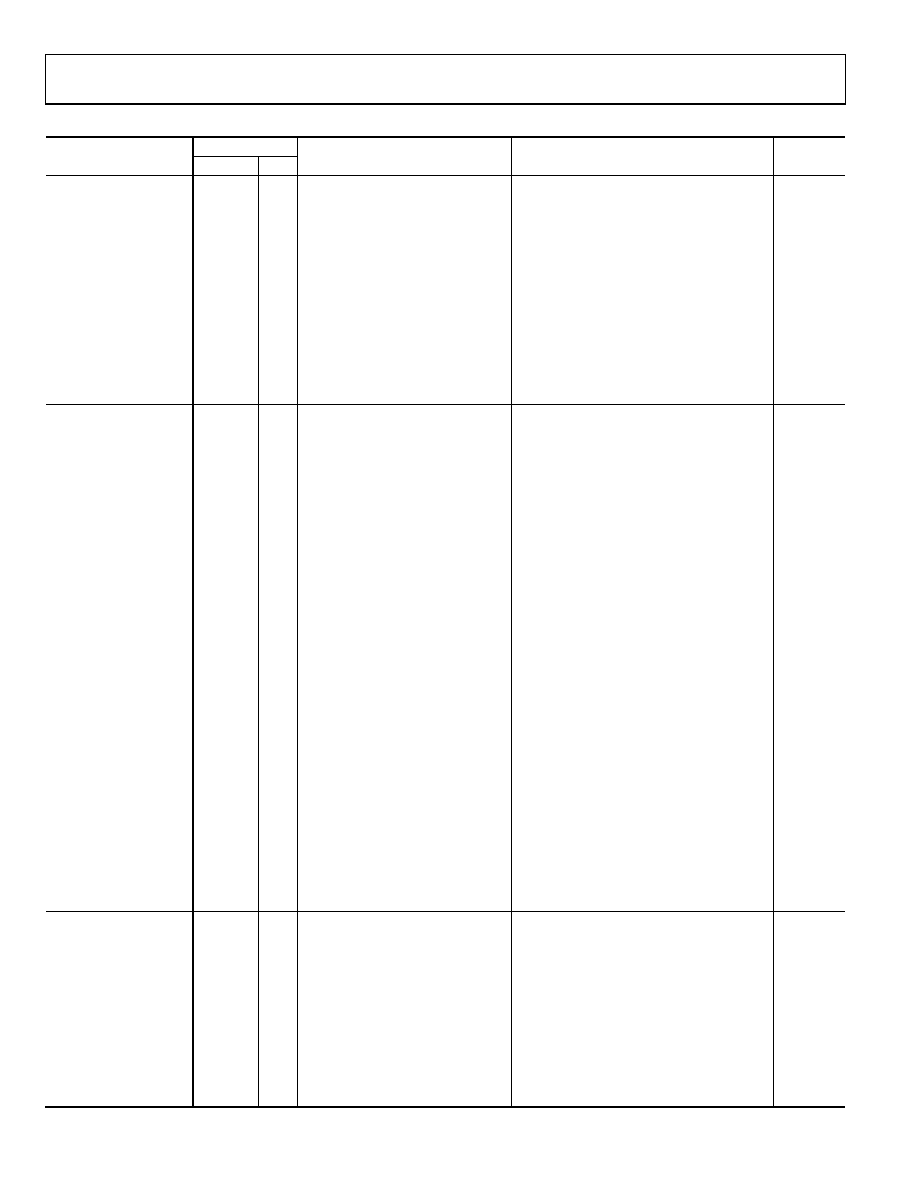

Table 12. SPI Register Description

Address

Register Name

Reg. No.

Bits

Description

Function

Default

Comm Register

00

7

SDIO bidirectional

0: use SDIO pin as input data only

0

1: use SDIO as both input and output data

00

6

LSB/MSB first

0: first bit of serial data is MSB of data byte

0

1: first bit of serial data is LSB of data byte

00

5

Software reset

Bit must be written with a 1, then 0 to soft

reset SPI register map

0

00

4

Power-down mode

0: all circuitry is active

1: disable all digital and analog circuitry,

only SPI port is active

00

3

Auto power-down enable

Controls auto power-down mode, see the

Power-Down and Sleep Modes section

0

00

1

PLL lock (read only)

0: PLL is not locked

1: PLL is locked

0

Digital Control Register

01

7:6

Filter interpolation factor

00: 1× interpolation

00

01: 2× interpolation

10: 4× interpolation

11: 8× interpolation

01

5:2

Filter modulation mode

See Table 21 for filter modes

0000

01

0

Zero stuffing

0: zero stuffing off

0

1: zero stuffing on

02

7

Data format

0: signed binary

0

1: unsigned binary

02

6

Dual/interleaved data bus mode

0: both input data ports receive data

0

1: Data Port 1 only receives data

02

5

Real mode

0: enable Q path for signal processing

0

1: disable Q path data (internal Q channel

clocks disabled, I and Q modulators

disabled)

02

4

DATACLK delay enable

See the Using Data Delay to Meet Timing

Requirements section.

02

3

Inverse sinc enable

0: inverse sinc filter disabled

0

1: inverse sinc filter enabled

02

2

DATACLK invert

0: output DATACLK same phase as internal

capture clock

0

1: output DATACLK opposite phase as

internal capture clock

02

1

TxEnable invert

Inverts the function of TxEnable Pin 39, see

the Interleaved Data Mode section

0

02

0

Q first

0: first byte of data is always I data at

beginning of transmit

1: first byte of data is always Q data at

beginning of transmit

Sync Control Register

03

7:6

Data clock delay mode

00: manual

00

03

5:4

Extra data clock divide ratio

Data clock output divider (see Table 22 for

divider ratio)

00

03

3:0

Reserved

000

04

7:4

Data clock delay

Sets delay of REFCLK in to DATACLK out

0000

04

3:1

Output sync pulse divide

Sets frequency of SYNC_O pulses

000

04

0

Sync out delay

Sync output delay, Bit 4

05

7:4

Sync out delay

Sync output delay, Bits<3:0>

0

05

3:1

Input sync pulse frequency

Input sync pulse frequency divider, see the

AN-822 application note

000

05

0

Sync input delay

Sync input delay, Bit 4

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| NCS2553DR2G | IC TRPL VIDEO AMP W/FILTER 8SOIC |

| VE-261-MY-B1 | CONVERTER MOD DC/DC 12V 50W |

| VE-260-MY-B1 | CONVERTER MOD DC/DC 5V 50W |

| AD5391BCPZ-5-REEL7 | IC DAC 12BIT 16CHAN 5V 64LFCSP |

| AD5391BCPZ-5-REEL | IC DAC 12BIT 16CHAN 5V 64-LFCSP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9776-EB | 制造商:Analog Devices 功能描述:AD9776 EVAL BOARD - Bulk |

| AD9776-EBZ | 制造商:Analog Devices 功能描述:DUAL 12B, 1.0 GSPS TXDAC - Bulk |

| AD9777 | 制造商:AD 制造商全稱:Analog Devices 功能描述:400 MHz to 6 GHz Broadband Quadrature Modulator |

| AD9777BSV | 制造商:Analog Devices 功能描述:DAC 2-CH R-2R 16-bit 80-Pin TQFP EP 制造商:Rochester Electronics LLC 功能描述:16BIT 160 MSPS DUAL TXDAC+ D/A CONVERTER - Bulk 制造商:Analog Devices 功能描述:Digital-Analog Converter IC Interface Ty |

| AD9777BSVRL | 制造商:Analog Devices 功能描述:DAC 2-CH R-2R 16-bit 80-Pin TQFP EP T/R |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。