- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4069 > CS80C286-12 (Intersil)IC CPU 16BIT 5V 12.5MHZ 68-PLCC PDF資料下載

參數(shù)資料

| 型號: | CS80C286-12 |

| 廠商: | Intersil |

| 文件頁數(shù): | 46/60頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC CPU 16BIT 5V 12.5MHZ 68-PLCC |

| 標(biāo)準(zhǔn)包裝: | 126 |

| 處理器類型: | 80C286 16-位 |

| 速度: | 12.5MHz |

| 電壓: | 5V |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 68-LCC(J 形引線) |

| 供應(yīng)商設(shè)備封裝: | 68-PLCC(24.23x24.23) |

| 包裝: | 管件 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁當(dāng)前第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

50

ASSUMING WORD-ALIGNED MEMORY OPERAND. IF ODD ALIGNED, 80C286 TRANSFERS TO/FROM MEMORY BYTE-AT-A-TIME WITH TWO MEMORY

CYCLES.

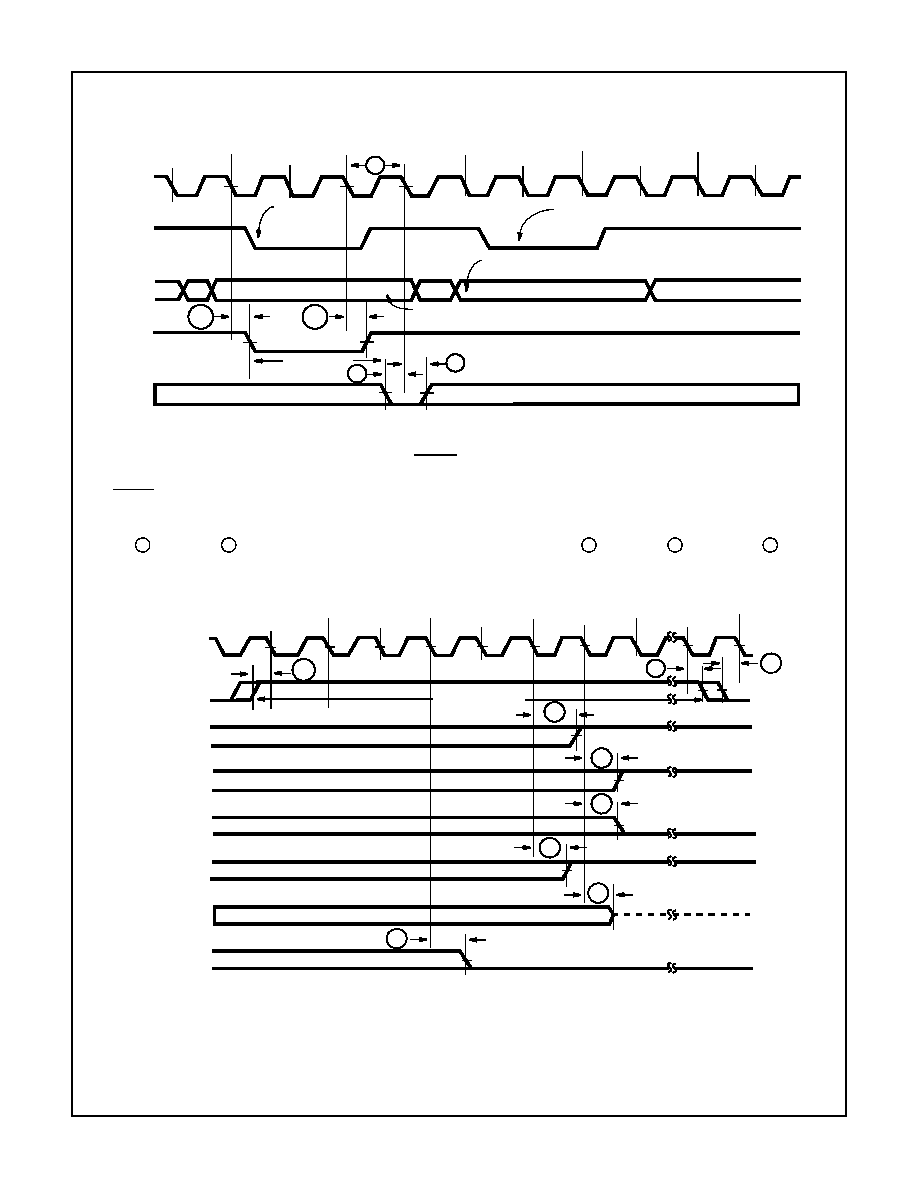

FIGURE 38. 80C286 PEREQ/PEACK TIMING FOR ONE TRANSFER ONLY

NOTES:

54. PEACK always goes active during the first bus operation of a processor extension data operand transfer sequence. The first bus opera-

tion will be either a memory read at operand address or I/O read at port address 00FA(H).

55. To prevent a second processor extension data operand transfer, the worst case maximum time (Shown above) is

3 x

- 12AMAX -

MIN. The actual configuration dependent, maximum time is: 3 x

- 12AMAX -

MIN + N x 2 x

. N is the

number of extra TC states added to either the first or second bus operation of the processor extension data operand transfer sequence.

FIGURE 39. INITIAL 80C286 PIN STATE DURING RESET

NOTES:

56. Setup time for RESET

↑ may be violated with the consideration that φ1 of the processor clock may begin one system CLK period later.

57. Setup and hold times for RESET

↓ must be met for proper operation, but RESET ↓ may occur during φ1 or φ2.

58. The data bus is only guaranteed to be in a high impedance state at the time shown.

Waveforms (Continued)

1

12A

12B

4

5

TI

φ2

BUS

CYCLE TYPE

VCH

CLK

VCL

φ1

S1

S0

A23 - A0

M/IO,

PEACK

PEREQ

φ2

φ1

φ2

φ1

φ2

φ1

TS

TC

TS

TC

TI

I/O READ IF PROC. EXT. TO MEMORY

MEMORY READ IF MEMORY TO PROC. EXT.

MEMORY WRITE IF PROC. EXT. TO MEMORY

I/O WRITE IF MEMORY TO PROC. EXT.

MEMORY ADDRESS IF PROC. EXT. TO MEMORY TRANSFER I/O PORT

ADDRESS 00FA(H) IF MEMORY TO PROC. EXT. TRANSFER

I/O PORT ADDRESS 00FA(H) IF PROC. EXT. TO MEMORY TRANSFER

MEMORY ADDRESS IF MEMORY TO PROC. EXT. TRANSFER

(SEE NOTE 54)

(SEE NOTE 55)

COD INTA

1

4

1

4

1

6

7

12B

13

15

16

19

φ2

BUS

CYCLE TYPE

VCH

CLK

VCL

φ1

RESET

A23 - A0

(SEE NOTE 56)

φ2

φ1

φ2

φ1

φ2

φ1

φ2

UNKNOWN

S1

S0

BHE

M/IO

COD/INTA

LOCK

DATA

HLDA

PEACK

TX

TI

AT LEAST

(SEE NOTE 57)

(SEE NOTE 58)

16 CLK PERIODS

80C286

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IP80C88 | IC CPU 8/16BIT 5V 5MHZ 40-DIP |

| SPC5200CBV400B | IC MPU 32BIT 500MHZ 272PBGA |

| ABB85DHBR | CONN EDGECARD 170PS R/A .050 SLD |

| XF2M-2215-1A | CONN FPC 22POS 0.5MM PITCH SMD |

| MPC859TCVR100A | IC MPU POWERQUICC 100MHZ 357PBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CS80C286-1296 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CS80C286-12X136 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CS80C286-16 | 功能描述:微處理器 - MPU CPU 16BIT 5V CMOS 16 MHZ 68PLCC COM RoHS:否 制造商:Atmel 處理器系列:SAMA5D31 核心:ARM Cortex A5 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:536 MHz 程序存儲器大小:32 KB 數(shù)據(jù) RAM 大小:128 KB 接口類型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作電源電壓:1.8 V to 3.3 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-324 |

| CS80C286-1696 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CS80C286-2 | 制造商:Harris Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。