- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄170347 > CYDD18S72V18-167BGI (CYPRESS SEMICONDUCTOR CORP) 256K X 72 DUAL-PORT SRAM, 9 ns, PBGA484 PDF資料下載

參數(shù)資料

| 型號: | CYDD18S72V18-167BGI |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | SRAM |

| 英文描述: | 256K X 72 DUAL-PORT SRAM, 9 ns, PBGA484 |

| 封裝: | 23 X 23 MM, 2.03 MM HEIGHT, 1 MM PITCH, PLASTIC, BGA-484 |

| 文件頁數(shù): | 21/53頁 |

| 文件大小: | 2422K |

| 代理商: | CYDD18S72V18-167BGI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁

FullFlex

Document #: 38-06072 Rev. *I

Page 28 of 53

10.00

5.00[34]

10.00

6.00[34]

10.00

ns

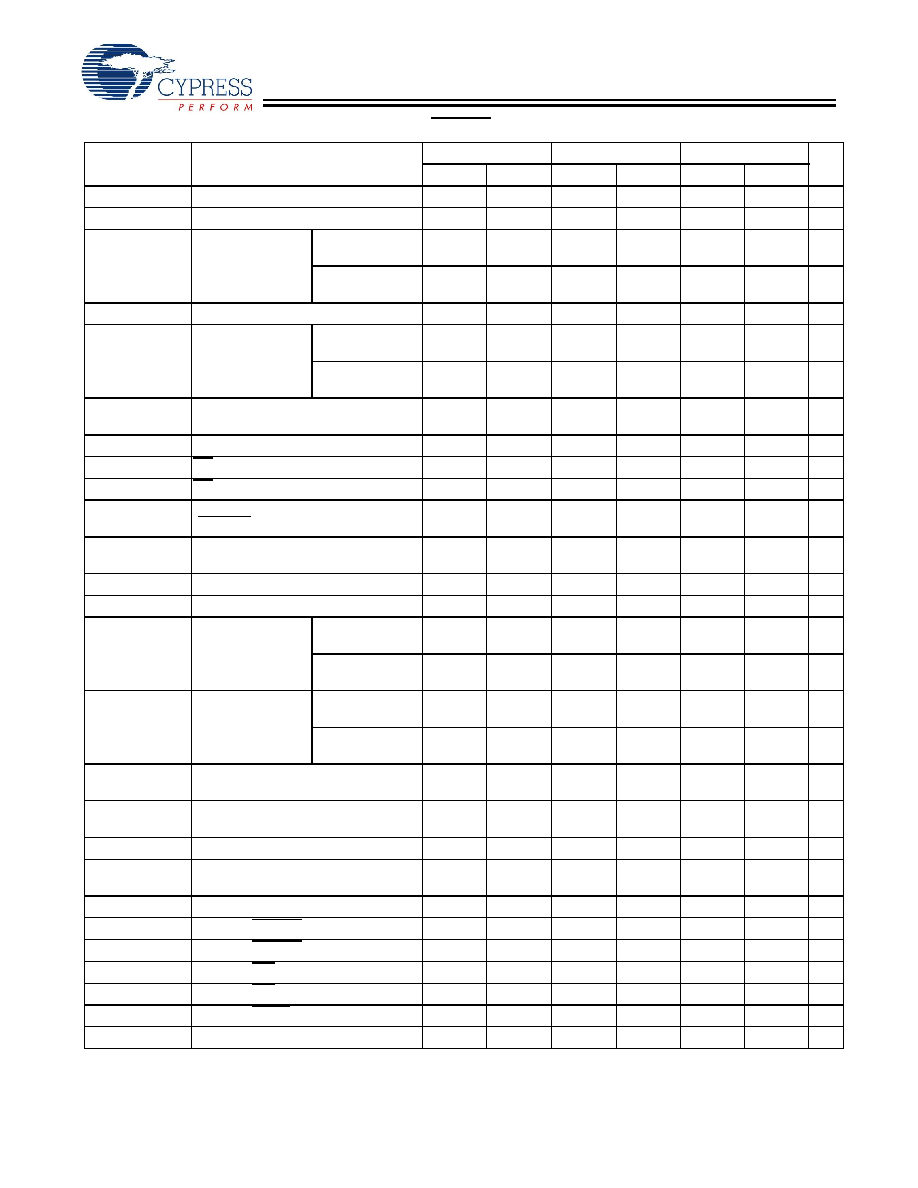

tCKD

C Clock Duty Time

45

55

45

55

45

55

%

tSD

Data Input Set-up

Time to C Rise

HSTL

1.8V LVCMOS

1.20[32,34]

1.50[32,34]

1.70[32,34]

ns

2.5V LVCMOS

3.3V LVTTL

1.45[32,34]

1.75[32,34]

1.95[32,34]

ns

tHD

Data Input Hold Time after C Rise

0.50

ns

tSAC

Address & Control

Input Set-up Time

to C Rise

HSTL

1.8V LVCMOS

1.20[32,34]

1.50[32,34]

1.70[32,34]

ns

2.5V LVCMOS

3.3V LVTTL

1.45[32,34]

1.75[32,34]

1.95[32,34]

ns

tHAC

Address & Control Input Hold Time

after C Rise

0.50

0.60

ns

tOE

Output Enable to Data Valid

3.40[32,34]

4.40[32,34]

5.00[32,34] ns

tOLZ[31]

OE to Low Z

1.00

ns

tOHZ[31]

OE to High Z

1.00

3.40[32,34]

1.00

4.40[32,34]

1.00

5.00[32,34] ns

tCD2[35]

C Rise to DQ Valid for Pipelined Mode

(LowSPD = 1)

2.64[32,34]

3.30[32,34]

4.00[32,34] ns

tCA2

C Rise to Address Readback Valid for

Pipelined Mode

4.00[34]

5.00[34]

6.00[34]

ns

tDC[35]

DQ Output Hold after C Rise

1.00

ns

tCCQ[35]

C Rise to CQ Rise

1.00

2.64[34]

1.00

3.30[34]

1.00

4.00[34]

ns

tCQHQV[35]

Echo Clock (CQ)

High to Output Valid

HSTL

1.8V LVCMOS

0.60[32]

0.70[32]

0.80[32]

ns

2.5V LVCMOS

3.3V LVTTL

0.70[32]

0.80[32]

0.90[32]

ns

tCQHQX[35]

Echo Clock (CQ)

High to Output Hold

HSTL

1.8V LVCMOS

–0.60

–0.70

–0.80

ns

2.5V LVCMOS

3.3V LVTTL

–0.75

–0.85

–0.95

ns

tCKHZ2[31,35]

C Rise to DQ Output High Z in

Pipelined Mode

1.00

2.64 [32,

34]

1.00

3.30[32,34]

1.00

4.00[32,34] ns

tCKLZ2[31,35]

C Rise to DQ Output Low Z in

Pipelined Mode

1.00

ns

tAC

Address Output Hold after C Rise

1.00

ns

tCKHZA2[31]

C Rise to Address Output High Z for

Pipelined Mode

1.00

4.00[34]

1.00

5.00[34]

1.00

6.00[34]

ns

tCKLZA[31]

C Rise to Address Output Low Z

1.00

ns

tSCINT

C Rise to CNTINT Low

1.00

2.64[34]

1.00

3.30[34]

1.00

4.00[34]

ns

tRCINT

C Rise to CNTINT High

1.00

2.64[34]

1.00

3.30[34]

1.00

4.00[34]

ns

tSINT

C Rise to INT Low

0.50

6.00[34]

0.50

7.00[34]

0.50

8.00[34]

ns

tRINT

C Rise to INT High

0.50

6.00[34]

0.50

7.00[34]

0.50

8.00[34]

ns

tBSY

C Rise to BUSY Valid

1.00

2.64[34]

1.00

3.30[34]

1.00

4.00[34]

ns

tJIT

Clock Input Cycle to Cycle Jitter

+/- 200

ps

Table 16.SDR Mode with Pipeline Mode, DLL Enabled (LOWSPD-HIGH)[33] (continued)

Parameter

Description

–200[27]

–167[27]

–133

Unit

Min.

Max.

Min.

Max.

Min.

Max.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CYW2330ZITR | PLL FREQUENCY SYNTHESIZER, 2500 MHz, PDSO20 |

| CYW311OXCT | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| CZ23EH-FREQ-OUT23 | VCXO, CLOCK, 1.25 MHz - 65 MHz, CMOS/TTL OUTPUT |

| CZM4-2000 | VCO, 1950 MHz - 2800 MHz |

| CZSH5-40C | 2.5 A, 40 V, SILICON, RECTIFIER DIODE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CYDD18S72V18-200BBC | 制造商:Cypress Semiconductor 功能描述:SRAM SYNC DUAL 1.8V 18MBIT 256KX72 0.5NS 484BGA - Bulk |

| CYDD18S72V18-200BBXC | 功能描述:IC SRAM 18MBIT 200MHZ 256LFBGA RoHS:是 類別:集成電路 (IC) >> 存儲器 系列:- 標準包裝:1,000 系列:- 格式 - 存儲器:RAM 存儲器類型:移動 SDRAM 存儲容量:256M(8Mx32) 速度:133MHz 接口:并聯(lián) 電源電壓:1.7 V ~ 1.95 V 工作溫度:-40°C ~ 85°C 封裝/外殼:90-VFBGA 供應(yīng)商設(shè)備封裝:90-VFBGA(8x13) 包裝:帶卷 (TR) 其它名稱:557-1327-2 |

| CYDH2200E | 制造商:Cypress Semiconductor 功能描述:CPLD BOOT EEPROM PROGRAMMING KIT - Bulk |

| CYDIO48 | 制造商:Misc 功能描述: |

| CYDM064A08 | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:1.8V 4K/8K/16K x 16 and 8K/16K x 8 MoBL㈢ Dual-Port Static RAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。