- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376803 > DM9161A (Electronic Theatre Controls, Inc.) 10/100 MBPS FAST ETHEMET PHYSICAL LAYER SINGLE CHIP TRANSCEIVER PDF資料下載

參數(shù)資料

| 型號: | DM9161A |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 10/100 MBPS FAST ETHEMET PHYSICAL LAYER SINGLE CHIP TRANSCEIVER |

| 中文描述: | 10/100 Mbps快速以太網(wǎng)物理層單芯片收發(fā)器 |

| 文件頁數(shù): | 18/45頁 |

| 文件大小: | 1206K |

| 代理商: | DM9161A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當(dāng)前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁

19

Preliminary

Version: DM9161A-DS-P04

Jan.19,2005

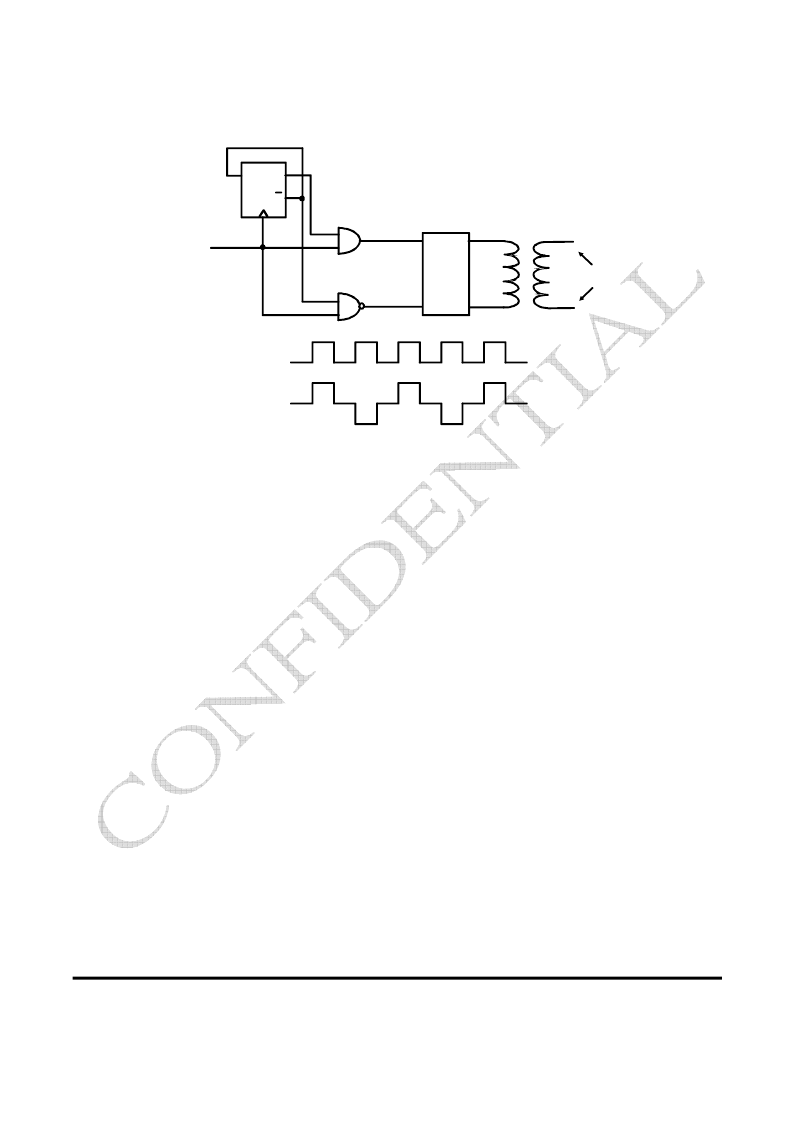

Figure 7-4

7.2.2 100Base-TX Receiver

The 100Base-TX receiver contains several function blocks

that convert the scrambled 125Mb/s serial data to

synchronous 4-bit nibble data, which is then provided to the

MII.

The receive section contains the following functional blocks:

- Signal Detect

- Adaptive Equalizer

- MLT-3 to NRZI Decoder

- Clock Recovery Module

- NRZI to NRZ Decoder

- Serial to Parallel

- Descrambler

- Code Group Alignment

- 4B5B Decoder

7.2.2.1 Signal Detect

The signal detect function meets the specifications

mandated by the ANSI XT12 TP-PMD 100Base-TX

Standards for both voltage thresholds and timing

parameters.

7.2.2.2 Adaptive Equalizer

When transmitting data at high speeds over copper twisted

pair cable, attenuation based on frequency becomes a

concern. In high speed twisted pair signaling, the frequency

content of the transmitted signal can vary greatly during

normal operation based on the randomness of the

scrambled data stream. This variation in signal attenuation

caused by frequency variations must be compensated for to

ensure the integrity of the received data. In order to ensure

quality transmission when employing MLT-3 encoding, the

compensation must be able to adapt to various cable lengths

and cable types depending on the installed environment.

The selection of long cable lengths for a given

implementation requires significant compensation, which will

be over-kill in a situation that includes shorter, less

attenuating cable lengths. Conversely, the selection of short

or intermediate cable lengths requiring less compensation

will cause serious under-compensation for longer length

cables. Therefore, the compensation or equalization must be

adaptive to ensure proper conditioning of the received signal

independent of the cable length.

7.2.2.3 MLT-3 to NRZI Decoder

The DM9161A decodes the MLT-3 information from the

Digital Adaptive Equalizer into NRZI data. The relation

between NRZI and MLT-3 data is shown in figure 7-4.

7.2.2.4 Clock Recovery Module

The Clock Recovery Module accepts NRZI data from the

MLT-3 to NRZI decoder. The Clock Recovery Module locks

D

CK

Q

Q

.

.

Binary

In

Common

driver

Binary minus

Binary plus

MLT-3

MLT-3

Binary

In

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DM9161AE | 10/100 MBPS FAST ETHEMET PHYSICAL LAYER SINGLE CHIP TRANSCEIVER |

| DM9161 | 10/100 Mbps FAST ETHERNET PHYSICAL LAYER SINGLE CHIP TRANSCEIVER |

| DM9161E | 10/100 Mbps FAST ETHERNET PHYSICAL LAYER SINGLE CHIP TRANSCEIVER |

| DM9301 | 100Mbps Ethernet Fiber/Twisted Pair Single Chip Media Converter |

| DM9301F | 100Mbps Ethernet Fiber/Twisted Pair Single Chip Media Converter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DM9161A_09 | 制造商:DAVICOM 制造商全稱:DAVICOM 功能描述:10/100 Mbps Fast Ethernet Physical Layer Single Chip Transceiver |

| DM9161AE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:10/100 MBPS FAST ETHEMET PHYSICAL LAYER SINGLE CHIP TRANSCEIVER |

| DM9161AEP | 制造商:DAVICOM 制造商全稱:DAVICOM 功能描述:10/100 Mbps Fast Ethernet Physical Layer Single Chip Transceiver |

| DM9161B | 制造商:DAVICOM 制造商全稱:DAVICOM 功能描述:10/100 Mbps Fast Ethernet Physical Layer Single Chip Transceiver |

| DM9161BEP | 制造商:DAVICOM 功能描述:IC TRX 10/100MBPS ENET PHY48LQFP 制造商:DAVICOM 功能描述:IC, TRX, 10/100MBPS, ENET PHY,48LQFP 制造商:DAVICOM 功能描述:IC, TRX, 10/100MBPS, ENET PHY,48LQFP; Data Rate:100Mbps; Ethernet Type:IEEE 802.3 / 802.3u; Supply Voltage Min:3.135V; Supply Voltage Max:3.465V; Digital IC Case Style:LQFP; No. of Pins:48; Interface Type:MII; Operating Temperature ;RoHS Compliant: Yes |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。