- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376803 > DM9161A (Electronic Theatre Controls, Inc.) 10/100 MBPS FAST ETHEMET PHYSICAL LAYER SINGLE CHIP TRANSCEIVER PDF資料下載

參數(shù)資料

| 型號: | DM9161A |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 10/100 MBPS FAST ETHEMET PHYSICAL LAYER SINGLE CHIP TRANSCEIVER |

| 中文描述: | 10/100 Mbps快速以太網(wǎng)物理層單芯片收發(fā)器 |

| 文件頁數(shù): | 6/45頁 |

| 文件大小: | 1206K |

| 代理商: | DM9161A |

第1頁第2頁第3頁第4頁第5頁當(dāng)前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁

Preliminary

6

Version: DM9161A-DS-P04

Jan.19, 2005

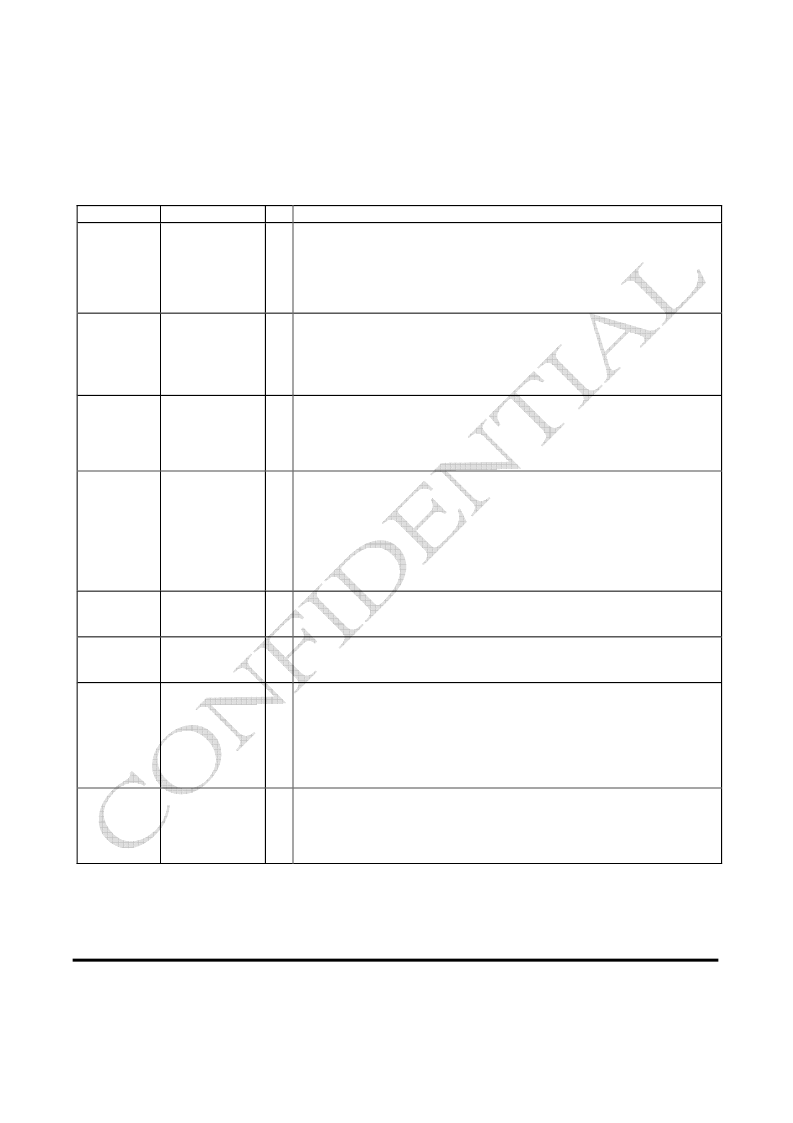

I: Input, O: Output, LI: Latch input when power-up/reset, Z: Tri-State output, U: Pulled high D: Pulled low

5.1 Normal MII Interface, 21 pins

Pin No.

Pin Name

I/O

16

TXER/TXD [4]

In 100Mbps mode, when the signal indicates active high and TXEN is

active, the HALT symbol substitutes the actual data nibble.

In 10Mbps, the input is ignored

In bypass mode (bypass BP4B5B), TXER becomes the TXD [4] pin, the

fifth TXD data bit of the 5B symbol

20,19,18,17

TXD [0:3]

I

Transmit Data

4-bit nibble data inputs (synchronous to the TXCLK) when in 10/100Mbps

nibble mode.

In 10Mbps GPSI (7-Wired) mode, the TXD [0] pin is used as the serial

data input pin, and TXD [1:3] are ignored.

Description

I

Transmit Error/The Fifth TXD Data Bit

21

TXEN

I

Transmit Enable

Active high indicates the presence of valid nibble data on the TXD [0:3] for

both 100Mbps and 10Mbps nibble modes.

In 10Mbps GPSI (7-Wired) mode, active high indicates the presence of

valid 10Mbps data on TXD [0].

Transmit Clock

The transmitting clock provides the timing reference for the transfer of the

TXEN, TXD, and TXER. TXCLK is provided by the PHY

25MHz in 100Mbps nibble mode, 2.5MHz in 10Mbps nibble mode, 10MHz

in 10Mbps GPSI (7-Wired) mode

ISOLATE Setting: (When power up reset, latch input)

0: Reg 0.10 will be initialized to “0”. (Ref.to 8.1 Basic Control Register)

1: Reg 0.10 will be initialized to “1”.

Management Data Clock

Synchronous clock for the MDIO management data. This clock is

provided by management entity, and it is up to 2.5MHz

I/O Management Data I/O

Bi-directional management data which may be provided by the station

management entity or the PHY

O,

Z,

LI

(D)

In 10Mbps GPSI (7-Wired) mode, the RXD [0] pin is used as the serial

data output pin, and the RXD [1:3] are ignored

PHY address [0:3] (power up reset latch input)

PHY address sensing input pins

IO,

LI

(D)

interrupt register [21] )

The interrupt output assert low when pull up.

Asserted high when pull down.

22

TXCLK/

ISOLATE

O,

Z,

LI

(D)

24

MDC

I

25

MDIO

29,28,27,26

RXD[0:3]

/PHYAD[0:3]

Receive Data Output

4-bit nibble data outputs (synchronous to RXCLK) when in 10/100Mbps

MII mode

32

MDINTR

Status Interrupt Output:

Whenever there is a status change (link, speed, duplex depend on

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DM9161AE | 10/100 MBPS FAST ETHEMET PHYSICAL LAYER SINGLE CHIP TRANSCEIVER |

| DM9161 | 10/100 Mbps FAST ETHERNET PHYSICAL LAYER SINGLE CHIP TRANSCEIVER |

| DM9161E | 10/100 Mbps FAST ETHERNET PHYSICAL LAYER SINGLE CHIP TRANSCEIVER |

| DM9301 | 100Mbps Ethernet Fiber/Twisted Pair Single Chip Media Converter |

| DM9301F | 100Mbps Ethernet Fiber/Twisted Pair Single Chip Media Converter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DM9161A_09 | 制造商:DAVICOM 制造商全稱:DAVICOM 功能描述:10/100 Mbps Fast Ethernet Physical Layer Single Chip Transceiver |

| DM9161AE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:10/100 MBPS FAST ETHEMET PHYSICAL LAYER SINGLE CHIP TRANSCEIVER |

| DM9161AEP | 制造商:DAVICOM 制造商全稱:DAVICOM 功能描述:10/100 Mbps Fast Ethernet Physical Layer Single Chip Transceiver |

| DM9161B | 制造商:DAVICOM 制造商全稱:DAVICOM 功能描述:10/100 Mbps Fast Ethernet Physical Layer Single Chip Transceiver |

| DM9161BEP | 制造商:DAVICOM 功能描述:IC TRX 10/100MBPS ENET PHY48LQFP 制造商:DAVICOM 功能描述:IC, TRX, 10/100MBPS, ENET PHY,48LQFP 制造商:DAVICOM 功能描述:IC, TRX, 10/100MBPS, ENET PHY,48LQFP; Data Rate:100Mbps; Ethernet Type:IEEE 802.3 / 802.3u; Supply Voltage Min:3.135V; Supply Voltage Max:3.465V; Digital IC Case Style:LQFP; No. of Pins:48; Interface Type:MII; Operating Temperature ;RoHS Compliant: Yes |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。