- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄376804 > DM9801E (Electronic Theatre Controls, Inc.) 1M home Phonrline Network Physical Layer Single Chip Transceiver PDF資料下載

參數(shù)資料

| 型號(hào): | DM9801E |

| 廠(chǎng)商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 1M home Phonrline Network Physical Layer Single Chip Transceiver |

| 中文描述: | 100萬(wàn)家庭Phonrline網(wǎng)絡(luò)物理層單芯片收發(fā)器 |

| 文件頁(yè)數(shù): | 4/61頁(yè) |

| 文件大小: | 589K |

| 代理商: | DM9801E |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)

DM9801

1M Home Phoneline Network Physical Layer Single Chip Transceiver

4

Preliminary

Version: DM9801-DS-P02

March 20, 2000

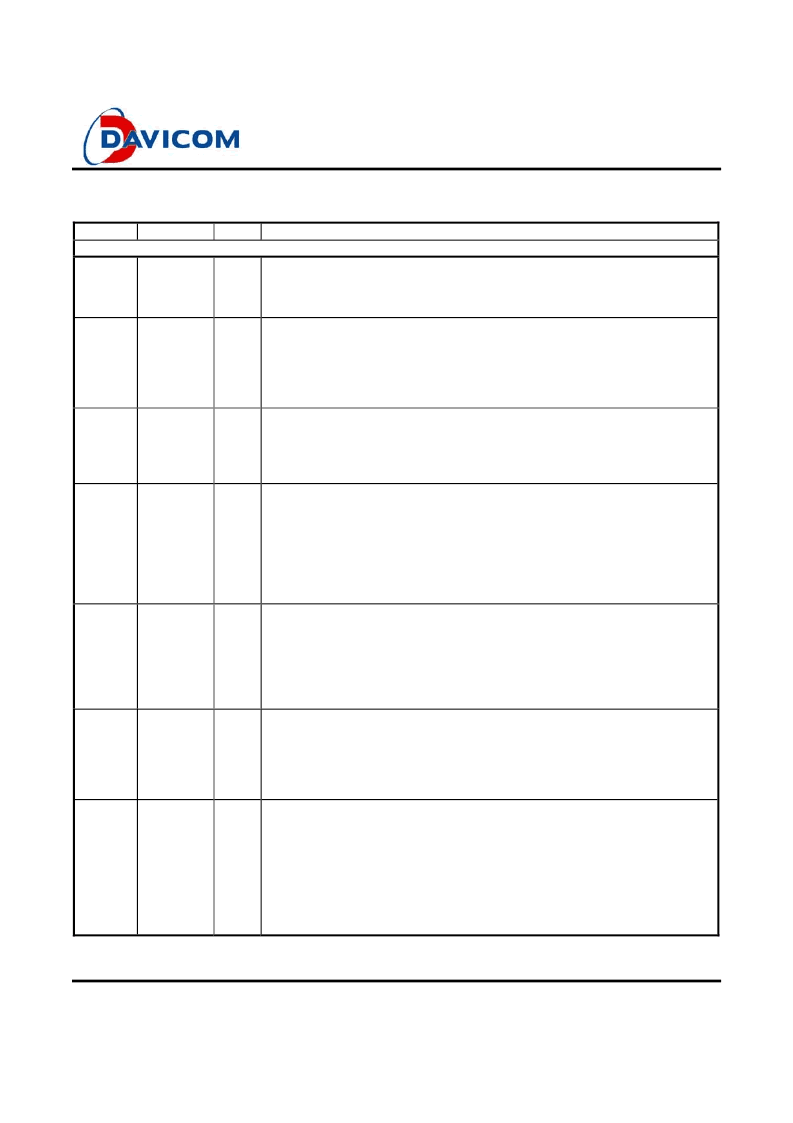

Pin Description

Pin No.

Station Interface: Receive Data, Transmit Data and Management

85

or

STXDAT

Transmit data input pin for serial data from the GPSI.

84

or

BP1

Most significant bit of a 2-bit encoded select. The BP1 and BP0 inputs, select

one of four, 64-byte, SPROM pages to initialize the DM9801 management

registers. Master mode must be selected using the SMODE input.

83

or

SI

This is the serial data input pin to the DM9801 for the SPI bus. The SPI bus

operation is only valid if GPSI mode is selected.

82

or

SMODE

This input pin selects the SPI buses mode of operation. The SPI bus modes

of operation are:

Master Mode (SMODE = 0)

Slave Mode (SMODE = 1)

The SPI bus operation is only valid if GPSI mode is selected.

86

or

STDCLK

mode.

Serial Transmit Data Clock (GPSI Mode, INTFSEL = 1):

STDCLK is an output from the DM9801. Used as the transmit reference clock

to clock in the STXDATA when in GPSI interface mode.

81

or

STXEN

Serial Transmit Enable (GPSI Mode, INTFSEL = 1):

Used to enable the transmit function of the GPSI when in GPSI interface

mode.

66

or

BP0

maximum clock rate is 2.5MHz.

SPROM Boot Page Select 0 (GPSI Mode, INTFSEL = 1):

Least significant bit of a 2-bit encoded select. The BP1 and BP0 inputs,

select one of four, 64-byte, SPROM pages to initialize the DM9801

management registers. Master mode must be selected using the SMODE

input.

Pin Name

I/O

Description

TXD0

I

Transmit Data Bit 0 (MII Mode, INTFSEL = 0):

Transmit data input pin, bit 0, for nibble data from the MII

Serial Transmit Data Bit (GPSI Mode, INTFSEL = 1):

TXD1

I

Transmit Data Bit 1 (MII Mode, INTFSEL = 0):

Transmit data input pin, bit 1, for nibble data from the MII

SPROM Boot Page Select 1 (GPSI Mode, INTFSEL = 1):

TXD2

I

Transmit Data Bit 2 (MII Mode, INTFSEL = 0):

Transmit data input pin, bit 2, for nibble data from the MII

Serial Data Input (GPSI Mode, INTFSEL = 1):

TXD3

I

Transmit Data Bit 3 (MII Mode, INTFSEL = 0):

Transmit data input pin, bit 3, for nibble data from the MII

Serial Mode Select (GPSI Mode, INTFSEL = 1):

TX_CLK

O,Z

MII Transmit Clock (MII Mode, INTFSEL = 0):

TX_CLK is an output pin from the DM9801. Used as the transmit data

reference clock, to clock in nibble data from the MII when in MII interface

TX_EN

I

MII Transmit Enable (MII Mode, INTFSEL = 0):

MII Transmit enable input, used to enable the transmit function of the MII

when in MII interface mode.

MDC

I

MII Serial Management Clock (MII Mode, INTFSEL = 0):

Synchronous clock to the MDIO management data input/output serial

interface which is asynchronous to transmit and receive clocks. The

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DMA2271 | Consumer IC |

| DMA2280 | Consumer IC |

| DMA2281 | Consumer IC |

| DMA2275 | DMA 2275, DMA 2286 C/D/D2-MAC Descrambler |

| DMA2286 | DMA 2275, DMA 2286 C/D/D2-MAC Descrambler |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DM9B | 功能描述:數(shù)字萬(wàn)用表 4000 COUNT AUTO RoHS:否 制造商:Tektronix 產(chǎn)品:Multimeters 類(lèi)型:Bench 準(zhǔn)確性:0.04 % 電壓范圍:2 V to 2 kV 電阻范圍: 電容范圍: 顯示計(jì)數(shù): 頻率:10 Hz to 45 Hz, 850 Hz to 1 MHz 測(cè)距: 真均方根值: 數(shù)據(jù)保持: |

| D-M9B | 制造商:SMC Corporation of America 功能描述:Sensor, solid state, direct mount, grommet connection, for MX/MH/CQ2/NCQ2/NCQ8 制造商:SMC 功能描述:2-Wire Auto Switch for 24Vdc Relay/PLC |

| D-M9BA | 制造商:SMC Corporation of America 功能描述:Autoswitch, water resistant, 2 wire, horizontal |

| D-M9BAL | 制造商:SMC Corporation of America 功能描述:AUTOSWITCH, DIRECT MT, SOLID STATE, GROMMET ENTRY, 3M LEADWIRE |

| D-M9BAVL | 制造商:SMC Corporation of America 功能描述:Autoswitch, water resistant, 2 wire, vertical |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。