- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377429 > IDT72V261LA (Integrated Device Technology, Inc.) 3.3 VOLT CMOS SuperSync FIFO PDF資料下載

參數(shù)資料

| 型號(hào): | IDT72V261LA |

| 廠商: | Integrated Device Technology, Inc. |

| 英文描述: | 3.3 VOLT CMOS SuperSync FIFO |

| 中文描述: | 3.3伏的CMOS SuperSync先進(jìn)先出 |

| 文件頁數(shù): | 27/27頁 |

| 文件大小: | 310K |

| 代理商: | IDT72V261LA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當(dāng)前第27頁

27

2002 Integrated Device Technology, Inc.

3.3 VOLT CMOS SuperSync FIFO

16,384 x 9

32,768 x 9

IDT72V261LA

IDT72V271LA

IDT and the IDT logo are registered trademarks. The SuperSync FIFO is a trademark of Integrated Device Technology, Inc.

COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

ADDENDUM

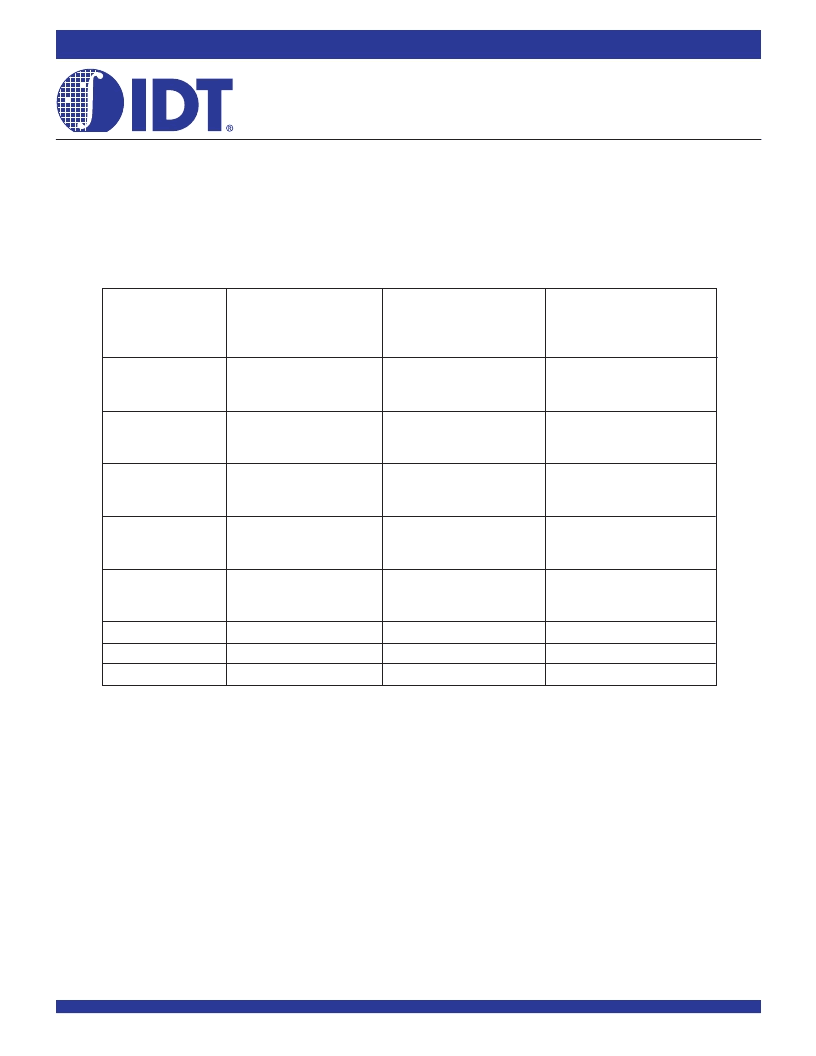

DIFFERENCES BETWEEN THE IDT72V261LA/72V271LA AND IDT72V261L/72V271L

IDT has improved the performance of the IDT72V261/72V271 SuperSync FIFOs. The new versions are designated by the “LA” mark. The LA

part is pin-for-pin compatible with the original “L” version. Some difference exist between the two versions. The following table details these differences.

Item

NEW PART

OLD PART

Comments

IDT72V261LA

IDT72V271LA

IDT72V261L

IDT72V271L

Pin #3

DC (Dont Care) - There is

no restriction on WCLK and

RCLK. See note 1.

60ns

(2)

+ t

REF

+ 1 T

RCLK

(4)

FS (Frequency Select)

In the LA part this pin must be tied

to either V

CC

or GND and must

not toggle after reset.

First word latency in the LA part is

a fixed value, independent of the

frequency of RCLK or WCLK.

First word latency in the LA part is

a fixed value, independent of the

frequency of RCLK or WCLK.

Retransmt latency in the LA part is

a fixed value, independent of the

frequency of RCLK or WCLK.

Retransmt latency in the LA part is

a fixed value, independent of the

frequency of RCLK or WCLK.

Active supply current

Standby current

Typical I

CC1

Current calculation

First Word Latency

(IDT Standard Mode)

t

FWL

1

= 10*Tf

(3)

+ 2T

RCLK

(4)

(ns)

First Word Latency

(FWFT Mode)

60ns

(2)

+ t

REF

+ 2 T

RCLK

(4)

t

FWL

2

= 10*Tf

(3)

+ 3T

RCLK

(4)

(ns)

Retransmt Latency

(IDT Standard Mode)

60ns

(2)

+ t

REF

+ 1 T

RCLK

(4)

t

RTF

1

= 14*Tf

(3)

+ 3T

RCLK

(4)

(ns)

Retransmt Latency

(FWFT Mode)

60ns

(2)

+ t

REF

+ 2 T

RCLK

(4)

t

RTF

2

= 14*Tf

(3)

+ 4T

RCLK

(4)

(ns)

I

CC1

I

CC2

Typical I

CC1

(5)

55mA

20mA

10 + 0.95*

S

+ 0.02*C

L

*f

S

(mA)

150mA

15mA

Not Given

NOTES:

1. WCLK and RCLK can vary independently and can be stopped. There is no restriction on operating WCLK and RCLK.

2. This is t

SKEW3

.

3. Tf is the period of the ‘selected clock’.

4. T

RCLK

is the cycle period of the read clock.

5. Typical I

CC1

is based on V

CC

= 3.3V, t

A

= 25

°

C, f

S

= WCLK frequency = RCLK frequency (in MHz using TTL levels), data switching at f

S

/2, C

L

= Capacitive Load (in pF).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IDT72V85L15PAG | 3.3 Volt CMOS DUAL ASYNCHRONOUS FIFO |

| IDT72V85L15PAGI | 3.3 Volt CMOS DUAL ASYNCHRONOUS FIFO |

| IDT72V85L20PAG | 3.3 Volt CMOS DUAL ASYNCHRONOUS FIFO |

| IDT72V85L20PAGI | 3.3 Volt CMOS DUAL ASYNCHRONOUS FIFO |

| IDT73720APQF | 16-BIT TRI-PORT BUS EXCHANGER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IDT72V261LA10PF | 功能描述:IC FIFO SS 8192X18 10NS 64QFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72V261LA10PF8 | 功能描述:IC FIFO SS 8192X18 10NS 64QFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72V261LA10PFG | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO SS 8192X18 10NS 64TQFP 制造商:Integrated Device Technology Inc 功能描述:IC FIFO 144K 16KX9 3.3V TQFP64 制造商:Integrated Device Technology Inc 功能描述:IC, FIFO, 144K, 16KX9, 3.3V, TQFP64 |

| IDT72V261LA10PFG8 | 制造商:Integrated Device Technology Inc 功能描述:IC FIFO SS 8192X18 10NS 64TQFP |

| IDT72V261LA10TF | 功能描述:IC FIFO SS 8192X18 10NS 64QFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標(biāo)準(zhǔn)包裝:90 系列:7200 功能:同步 存儲(chǔ)容量:288K(16K x 18) 數(shù)據(jù)速率:100MHz 訪問時(shí)間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應(yīng)商設(shè)備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。