- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄45377 > IR80C52CXXX-12:RD (TEMIC SEMICONDUCTORS) 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CQCC44 PDF資料下載

參數(shù)資料

| 型號(hào): | IR80C52CXXX-12:RD |

| 廠商: | TEMIC SEMICONDUCTORS |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CQCC44 |

| 文件頁(yè)數(shù): | 41/101頁(yè) |

| 文件大?。?/td> | 3398K |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)當(dāng)前第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)

AT86RF212

6 Functional Description

6.1 Introduction – IEEE 802.15.4-2006 Frame Format

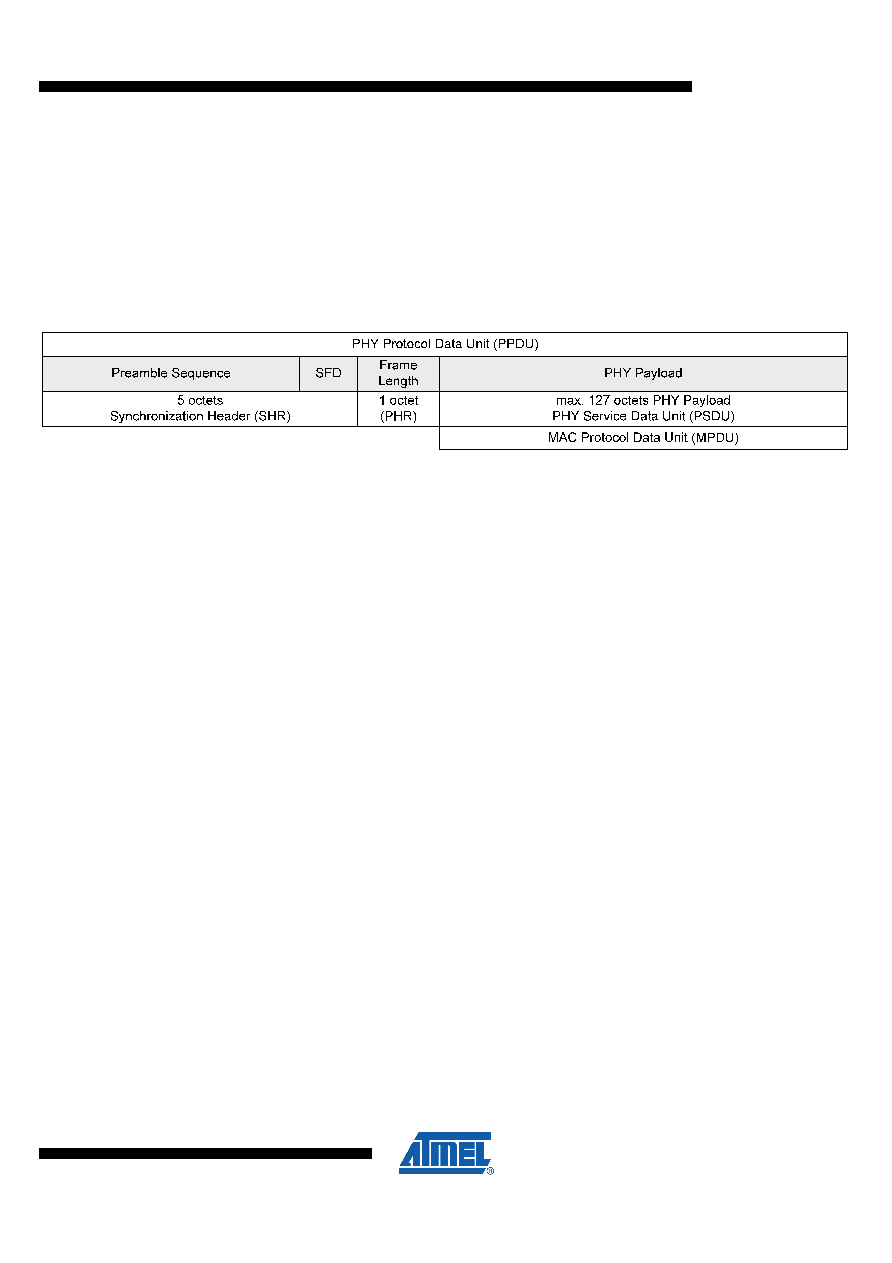

Figure 6-1 provides an overview of the physical layer (PHY) frame structure as defined

by the IEEE 802.15.4-2006 standard. Figure 6-2 shows the medium access control

layer (MAC) frame structure.

Figure 6-1. IEEE 802.15.4 Frame Format – PHY Layer Frame Structure

6.1.1 PHY Protocol Data Unit (PPDU)

6.1.1.1 Synchronization Header (SHR)

The SHR consists of a four-octet preamble field (all zero), followed by a single octet

start-of-frame delimiter (SFD). During transmit, the SHR is automatically generated by

the AT86RF212, thus the Frame Buffer shall contain PHR and PSDU only, see section

The transmission of the SHR requires 40 symbols for a transmission with BPSK

modulation and 10 symbols for a transmission with O-QPSK modulation. Table 6-1

illustrates the SHR duration depending on the selected data rate, see also section 10.5.

As the SPI data rate is usually higher than the over-the-air data rate, this allows the

microcontroller to initiate a transmission before the frame buffer write access is

completed.

During frame reception, the SHR is used for synchronization purposes. The matching

SFD determines the beginning of the PHR and the following PSDU payload data.

6.1.1.2 PHY Header (PHR)

The PHY header is a single octet following the SHR. The least significant 7 bits denote

the frame length of the following PSDU, while the most significant bit of that octet is

reserved and shall be set to 0 for IEEE 802.15.4 compliant frames. Even though the

MSB is reserved, AT86RF212 is able to transmit and receive this bit.

In transmit mode, the PHR needs to be supplied as the first octet during Frame Buffer

write access, see section 4.3.2.

In receive mode, the PHR is returned as the first octet during Frame Buffer read

access, see section 4.3.2.

6.1.1.3 PHY Payload (PHY Service Data Unit, PSDU)

The PSDU has a variable length between one and 127 octets. The PSDU contains the

MAC protocol data unit (MPDU), where the last two octets are used for the Frame

Check Sequence (FCS), see section 6.3.

67

8168C-MCU Wireless-02/10

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IS83C154TXXX-25D | 8-BIT, MROM, 25 MHz, MICROCONTROLLER, PQCC44 |

| IF180C52EXXX-L16:R | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP44 |

| MQ80C52CXXX-20/883R | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, CQFP44 |

| MJ80C31U-36:D | MICROCONTROLLER |

| R80C52XXX-12SHXXX | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, CQCC44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IR80C86-2 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:16-Bit Microprocessor |

| IR80C88 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:16-Bit Microprocessor |

| IR80C88-2 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:16-Bit Microprocessor |

| IR-820 | 制造商:BOWEI 制造商全稱(chēng):BOWEI 功能描述:Image Rejection Mixers |

| IR8200 | 制造商:IRF 制造商全稱(chēng):International Rectifier 功能描述:3A, 55V DMOS H-BRIDGE |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。