- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄224103 > K7R163684B (SAMSUNG SEMICONDUCTOR CO. LTD.) 512Kx36 & 1Mx18 QDR II b4 SRAM PDF資料下載

參數(shù)資料

| 型號: | K7R163684B |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 512Kx36 & 1Mx18 QDR II b4 SRAM |

| 中文描述: | 512Kx36 |

| 文件頁數(shù): | 11/18頁 |

| 文件大?。?/td> | 418K |

| 代理商: | K7R163684B |

- 2 -

Rev 3.1

July. 2004

512Kx36 & 1Mx18 QDRTM II b4 SRAM

K7R163684B

K7R161884B

36 (or 18)

Q(Data Out)

(Echo Clock out)

CQ, CQ

72

512Kx36-bit, 1Mx18-bit QDRTM II b4 SRAM

FEATURES

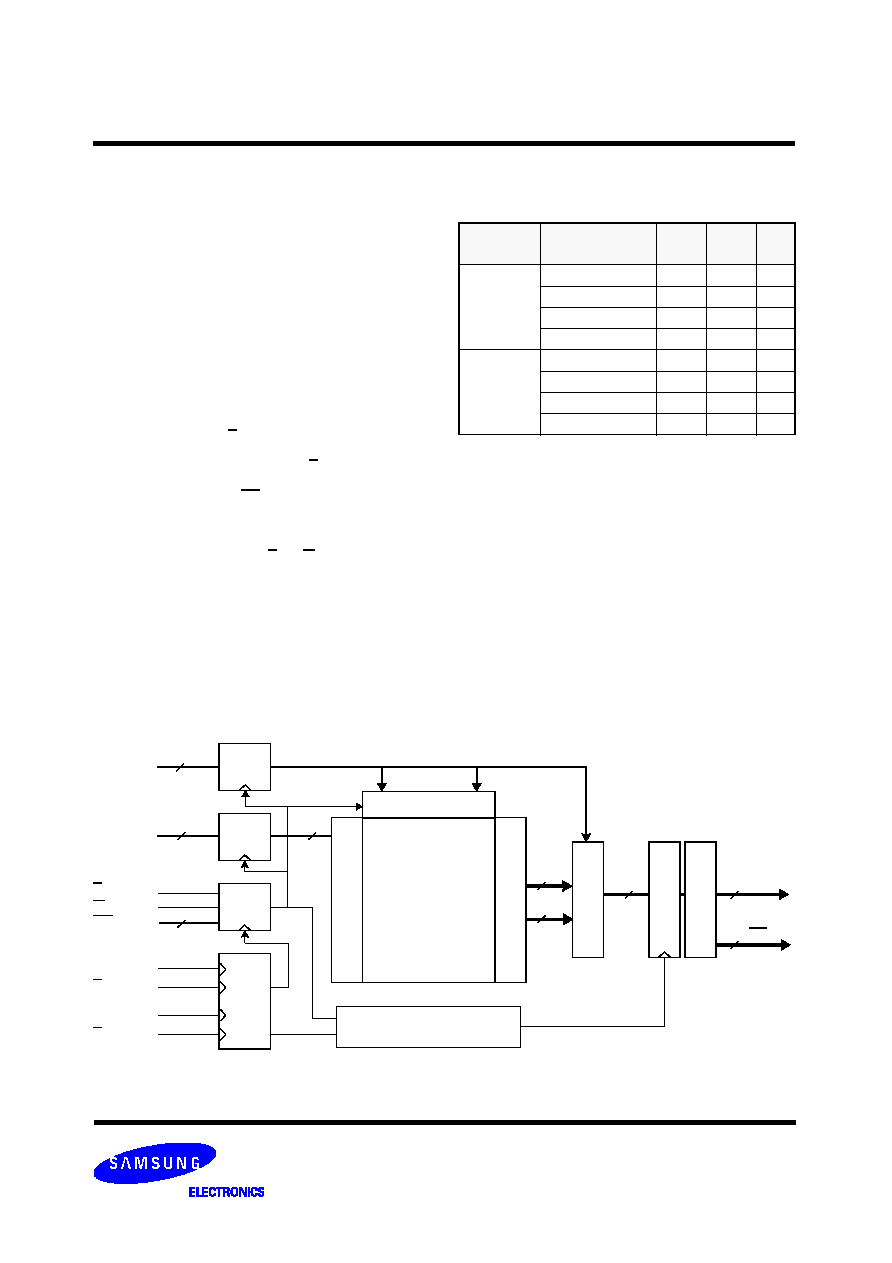

FUNCTIONAL BLOCK DIAGRAM

1.8V+0.1V/-0.1V Power Supply.

DLL circuitry for wide output data valid window and future

freguency scaling.

I/O Supply Voltage 1.5V+0.1V/-0.1V for 1.5V I/O,

1.8V+0.1V/-0.1V for 1.8V I/O

.

Separate independent read and write data ports

with concurrent read and write operation

HSTL I/O

Full data coherency, providing most current data .

Synchronous pipeline read with self timed late write.

Registered address, control and data input/output.

DDR(Double Data Rate) Interface on read and write ports.

Fixed 4-bit burst for both read and write operation.

Clock-stop supports to reduce current.

Two input clocks(K and K) for accurate DDR timing at clock

rising edges only.

Two input clocks for output data(C and C) to minimize

clock-skew and flight-time mismatches.

Two echo clocks (CQ and CQ) to enhance output data

traceability.

Single address bus.

Byte write (x18, x36) function.

Sepatate read/write control pin(R and W)

Simple depth expansion with no data contention.

Programmable output impenance.

JTAG 1149.1 compatible test access port.

165FBGA(11x15 ball array FBGA) with body size of 13x15mm

R

ADDRESS

W

C

D(Data in)

ADD

REG

DATA

REG

CLK

GEN

CTRL

LOGIC

512Kx36

(1Mx18)

MEMORY

ARRAY

WRITE DRIVER

K

BWX

36 (or 18)

SELECT OUTPUT CONTROL

SEN

SE

A

M

PS

W

R

IT

E

/RE

AD

DE

C

O

D

E

OUT

P

UT

RE

G

OUT

P

UT

S

E

L

E

CT

OUT

P

UT

DRIV

E

R

Notes: 1. Numbers in ( ) are for x18 device

72

17

17 (or 18)

4 (or 2)

72(or 36)

144

Organization

Part

Number

Cycle

Time

Access

Time

Unit

X36

K7R163684B-FC30

3.3

0.45

ns

K7R163684B-FC25

4.0

0.45

ns

K7R163684B-FC20

5.0

0.45

ns

K7R163684B-FC16

6.0

0.50

ns

X18

K7R161884B-FC30

3.3

0.45

ns

K7R161884B-FC25

4.0

0.45

ns

K7R161884B-FC20

5.0

0.45

ns

K7R161884B-FC16

6.0

0.50

ns

QDR SRAM and Quad Data Rate comprise a new family of products developed by Cypress, Renesas, IDT, NEC and Samsung technology.

(or 18)

(or 36)

(or 72)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K7R323682 | 1Mx36 & 2Mx18 & 4Mx9 QDRTM II b2 SRAM |

| K971 | 85.05 mm2, COPPER ALLOY, TIN FINISH, RING TERMINAL |

| K972 | 85.05 mm2, COPPER ALLOY, TIN FINISH, RING TERMINAL |

| K973 | 85.05 mm2, COPPER ALLOY, TIN FINISH, RING TERMINAL |

| KBJ402G | 4 A, 200 V, SILICON, BRIDGE RECTIFIER DIODE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K7R163684B_06 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512Kx36 & 1Mx18 QDRTM II b4 SRAM |

| K7R163684B-FC16 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512Kx36 & 1Mx18 QDR II b4 SRAM |

| K7R163684B-FC20 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512Kx36 & 1Mx18 QDR II b4 SRAM |

| K7R163684B-FC20000 | 制造商:Samsung Semiconductor 功能描述:SRAM Chip Sync Single 1.8V 18M-Bit 512K x 36 0.45ns 165-Pin FBGA |

| K7R163684B-FC25 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:512Kx36 & 1Mx18 QDR II b4 SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。