- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367558 > LH7A405 Microcontroller PDF資料下載

參數(shù)資料

| 型號(hào): | LH7A405 |

| 英文描述: | Microcontroller |

| 中文描述: | 微控制器 |

| 文件頁數(shù): | 6/53頁 |

| 文件大小: | 396K |

| 代理商: | LH7A405 |

第1頁第2頁第3頁第4頁第5頁當(dāng)前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁

LH7A405

32-Bit System-on-Chip

6

Advance Data Sheet

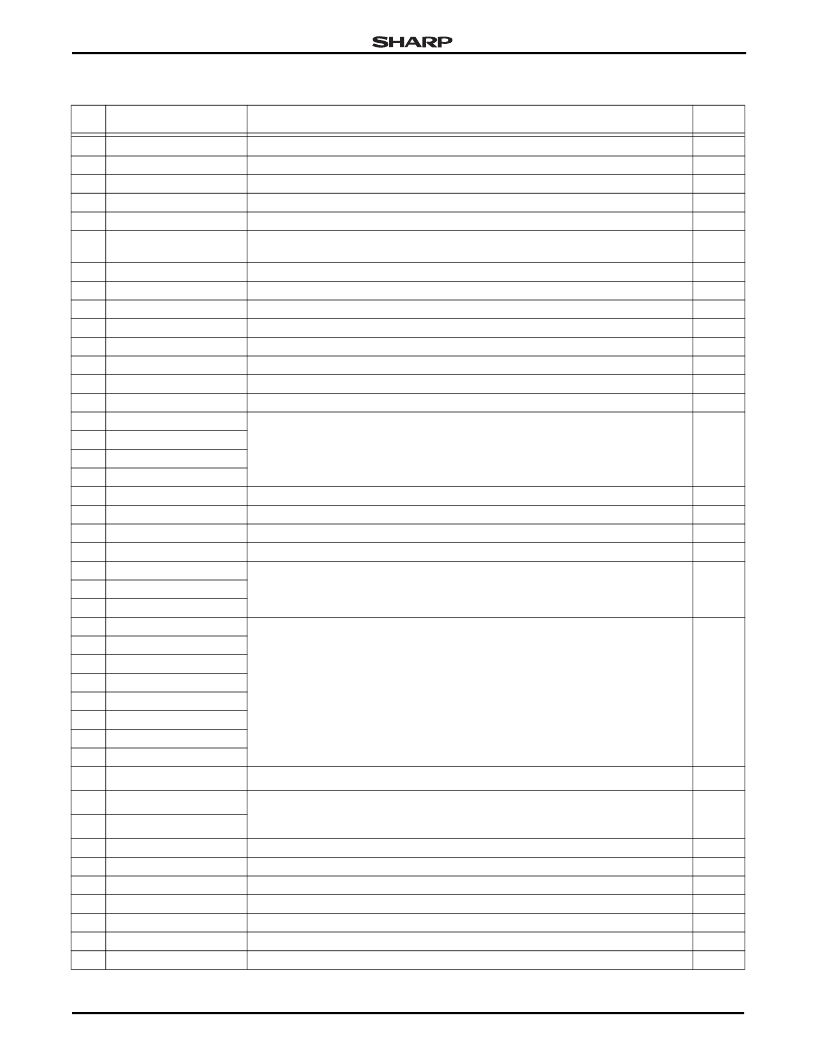

AB2

PG4/nCFREG

GPIO Port G/Compact Flash Register memory access

8 mA

AA3

PG5/nCFCE1

GPIO Port G/Compact Flash Chip Enable 1

8 mA

AB3

PG6/nCFCE2

GPIO Port G/Compact Flash Chip Enable 2

8 mA

Y3

PG7/PCDIR

GPIO Port G/PC Card Direction

8 mA

AB4

PH0/CFRESETA

GPIO Port H/Compact Flash Reset A

8 mA

AA4

PH1/CFA8/CFA24/

CFRESETB

GPIO Port H/Compact Flash Address Bit 8/PCMCIA1 Address Bit 24/PCMCIA2 Reset B

8 mA

Y4

PH2/nCFENA

GPIO Port H/Compact Flash Enable A

8 mA

AB5

PH3/CFA9/CFA25/nCFENB GPIO Port H/Compact Flash Address Bit 9/PCMCIA1 Address Bit 25/PCMCIA2 Enable B

8 mA

AA5

PH4/nCFWAIT/nCFWAITA

GPIO Port H/Compact Flash WAIT Signal/PCMCIA WAIT A

8 mA

W5

PH5/CFA10/nCFWAITB

GPIO Port H/Compact Flash Address Bit 10/PCMCIA2 WAIT B

8 mA

AB6

PH6/AC97RESET

GPIO Port H/AC97 reset

8 mA

Y6

PH7/nCFSTATEN

GPIO Port H/Compact Flash Status Read Enable

8 mA

W6

LCDCLKIN

External Clock Input for LCD controller

AB7

nBLE2

Byte Lane Enable 2

16 mA

AA7

LCDVD0

LCD Video Data Interface

16 mA

Y7

LCDVD1

W7

LCDVD2

AB8

LCDVD3

AA8

PE0/LCDVD4

GPIO Port E and LCD Video Data Interface

16 mA

Y8

nBLE1

Byte Lane Enable 1

16 mA

P10

LCDM

AC bias for LCD. This signal is used on STN displays

16 mA

AB9

LCDDCLK

LCD Pixel Clock

16 mA

AA9

PE1/LCDVD5

GPIO Port E and LCD Video Data Interface

16 mA

Y9

PE2/LCDVD6

W9

PE3/LCDVD7

AB10 PD0/LCDVD8

GPIO Port D and LCD Video Data Interface

16 mA

AA10 PD1/LCDVD9

Y10

PD2/LCDVD10

W10

PD3/LCDVD11

AB11 PD4/LCDVD12

AA11 PD5/LCDVD13

Y11

PD6/LCDVD14

AB12 PD7/LCDVD15

AA12 BATCNTL

Battery Control for A/D controller battery monitor.

16 mA

N11

BOOTWIDTH0

Boot Width Pins. Used with the MEDCHG bit. On power up, the values on these pins are

latched to determine the width and type of Boot device. Boot width can be 8-, 16-, or 32-bit.

N12

BOOTWIDTH1

W12

LR_YM

Touch Screen Controller Lower Right Y-minus

AA13 AN1

A/D channel 1

Y13

AN6

A/D channel 6

W13

LL_YP

Touch Screen Controller Lower Left Y-plus

AB14 AN5

A/D channel 5

AA14 AN2

A/D channel 2

Y14

UR_XM

Touch Screen Controller Upper Right X-minus

Table 1. Functional Pin List (Cont’d)

BGA

SIGNAL

DESCRIPTION

OUTPUT

DRIVE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LH8001 | Microprocessor |

| LH8002 | Microprocessor |

| LH8010 | Peripheral IC |

| LH8030 | Telecommunication IC |

| LH8036 | Peripheral IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LH8000A-C | 制造商:Black Box Corporation 功能描述:DUAL SPEED 10/100 STACKABLE HUB CLIENT |

| LH8000A-C-W1 | 制造商:Black Box Corporation 功能描述:1 YEAR WARRANTY FOR LH8000A-C |

| LH8000A-C-W3 | 制造商:Black Box Corporation 功能描述:3 YEAR WARRANTY FOR LH8000A-C |

| LH8000A-M | 制造商:Black Box Corporation 功能描述:DUAL SPEED 10/100 STACKABLE HUB MASTER |

| LH8000A-M-SOL-W1 | 制造商:Black Box Corporation 功能描述:1 YEAR WARRANTY FOR LH8000A-M-SOL |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。