- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377798 > LXT6155 (Intel Corp.) 155 Mbps SDH/SONET/ATM Transceiver PDF資料下載

參數(shù)資料

| 型號: | LXT6155 |

| 廠商: | Intel Corp. |

| 英文描述: | 155 Mbps SDH/SONET/ATM Transceiver |

| 中文描述: | 155速率的SDH / SONET / ATM的收發(fā)器 |

| 文件頁數(shù): | 9/50頁 |

| 文件大?。?/td> | 291K |

| 代理商: | LXT6155 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當(dāng)前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁

Datasheet

9

155 Mbps SDH/SONET/ATM Transceiver — LXT6155

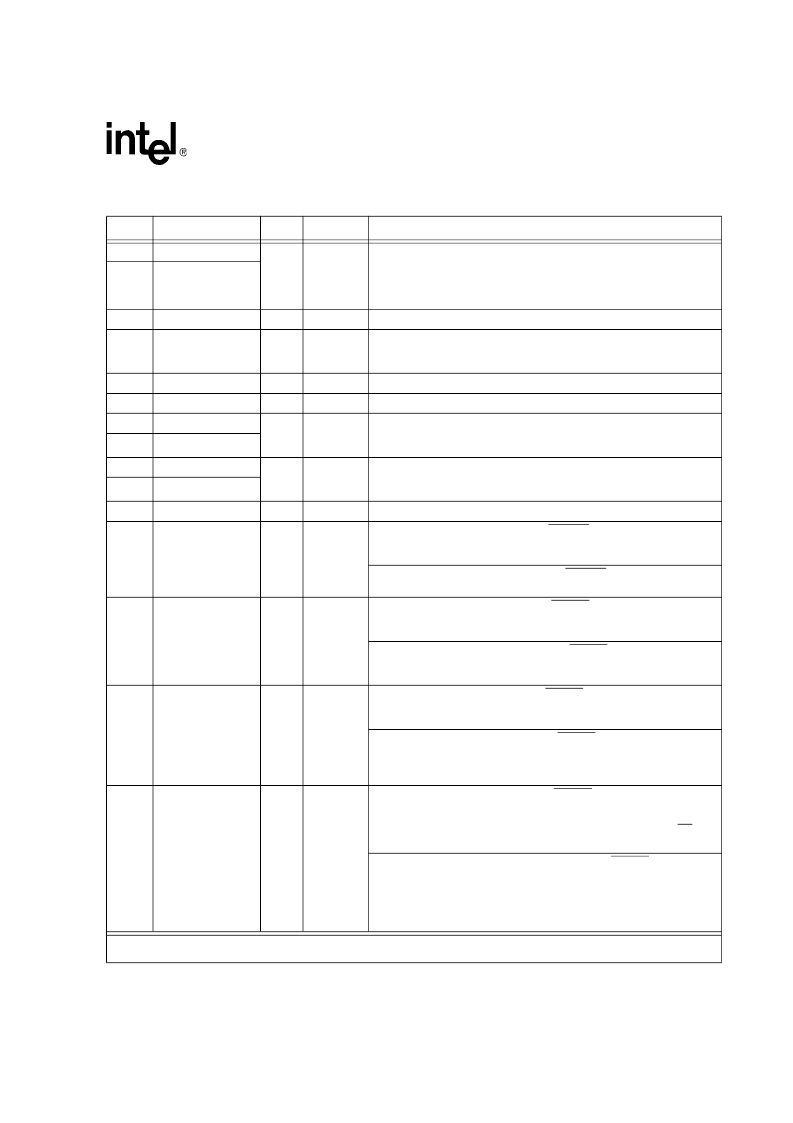

Table 1.

LXT6155 Pin Descriptions

Pin #

Symbol

I/O

1

Type

2

Description

1

XTALIN

AI/O

Crystal Input/Output

. These pins are connected to an external 19.44

MHz crystal. Alternately, a stable external clock signal may be connected

to XTALIN with XTALOUT left open. XTALIN should be connected to

TAGND and XTALOUT should be left open if the transmit input clock is

used as a clock reference

2

XTALOUT

3

TAGND

S

Transmit Analog Ground.

4

TXISH

AI/O

Transmit PLL Loop Filter Pin.

Connecting a capacitor to TAGND from

this pin controls the Tx PLL transfer function. This pin requires a 68nF

cap to TAGND.

5

TAVCC

S

Transmit Analog Power Supply.

6

TDVCC

S

Transmit Digital Power Supply.

7

TSICLKP

DI

LVPECL

Transmit Serial Input Clock, positive and negative

. Differential

Transmit clocks at 155.52 MHz. These pins are disabled when parallel

mode is selected.

8

TSICLKN

9

TPOS

DI

LVPECL

Transmit Serial Input Data, positive and negative.

Differential input

data from an overhead terminator at 155.52 Mbps, clocked in by TSICLK.

These pins are disabled when parallel mode is selected.

10

TNEG

11

TDGND

S

Transmit Digital Ground.

12

CS/MODE

DI

TTL

Chip Select Input, software mode

(HWSEL = High). Register

transactions through the

μ

P interface are initiated by the falling edge of

this signal.

Line Interface Mode, hardware mode

(HWSEL = Low). Sets line

interface mode to LVPECL (MODE = Low) or CMI (MODE = High).

13

SCLK/SP

DI

TTL

Serial Clock Input, software mode

(HWSEL = High). Serial

Microprocessor uses this pin to clock in/out data. SCLK can be from 0 to

4.096 MHz.

Serial/Parallel Select, hardware mode

(HWSEL = Low). When

SP = Low, serial systems interface is used. When SP = High, 8 bit

parallel system interface is used.

14

SDI/CIS

DI

TTL

Serial Input Data, software mode

(HWSEL = High). The serial data is

applied to this pin when the LXT6155 operates in software mode. SDI is

sampled on the rising edge of SCLK.

Clock Input Select, hardware mode

(HWSEL = Low). CIS sets the

reference clock for centering the Rx PLL. If CIS = Low, then the LXT6155

uses the transmit input clock as the reference. If CIS = High, then the

LXT6155 uses the crystal clock input (XTALIN) as the reference.

15

SDO/RIFE

DI/O

TTL

Serial Output Data, software mode

(HWSEL = High). The serial data

from the on-chip register is output on this pin in software mode. Data

output is valid on the rising edge of SCLK. This pin goes to a high

impedance state when the serial port is being written to or when CS is

High.

Receive Input Frame Enabler, hardware mode

(HWSEL = Low). The

frame detection option is available only in parallel mode. If RIFE = Low,

then the LXT6155 disables the frame detection, and byte alignment. If

RIFE = High, then the LXT6155 enables the frame detection, and outputs

RPOD bytes aligned to the SONET/SDH framer. This feature, if used,

must be enabled prior to applying data to Rtip/Rring.

1. DI = Digital Input; DO = Digital Output; DI/O = Digital Input/Output; AI = Analog Input; AO = Analog Output; AI/O = Analog Input/Output; S=Supply.

2. TTL = Transistor-to-Transistor Logic (5V tolerant); LVPECL = Low-Voltage positive ECL.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LXT6234 | E-Rate Multiplexer |

| LXT901 | 8QLYHUVDO (WKHUQHW 7UDQVFHLYHU |

| LXT901A | 8QLYHUVDO (WKHUQHW 7UDQVFHLYHU |

| LXT907A | 8QLYHUVDO (WKHUQHW 7UDQVFHLYHU |

| LXT902 | Ethernet Twisted-Pair Media Attachment Unit |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LXT6155LE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecomm/Datacomm |

| LXT6234 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:E-Rate Multiplexer |

| LXT6251A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ATM/SONET MAPPER|CMOS|QFP|208PIN|PLASTIC |

| LXT901 | 制造商:LVL1 制造商全稱:LVL1 功能描述:8QLYHUVDO (WKHUQHW 7UDQVFHLYHU |

| LXT901/LXT907 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LXT901. LXT907 - Design Guide for LXT901/907 Ethernet Interface Connection to Motorola MC68EN360 Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。