- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377801 > M12L64322A-7BG (ELITE SEMICONDUCTOR MEMORY TECHNOLOGY INC) 512K x 32 Bit x 4 Banks Synchronous DRAM PDF資料下載

參數(shù)資料

| 型號: | M12L64322A-7BG |

| 廠商: | ELITE SEMICONDUCTOR MEMORY TECHNOLOGY INC |

| 元件分類: | DRAM |

| 英文描述: | 512K x 32 Bit x 4 Banks Synchronous DRAM |

| 中文描述: | 2M X 32 SYNCHRONOUS DRAM, 6 ns, PBGA90 |

| 封裝: | 8 X 13 MM, LEAD FREE, BGA-90 |

| 文件頁數(shù): | 8/47頁 |

| 文件大?。?/td> | 791K |

| 代理商: | M12L64322A-7BG |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當(dāng)前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁

ES MT

M12L64322A

Elite Semiconductor Memory Technology Inc.

Publication Date: Mar. 2007

Revision

:

2.3

8/47

Version

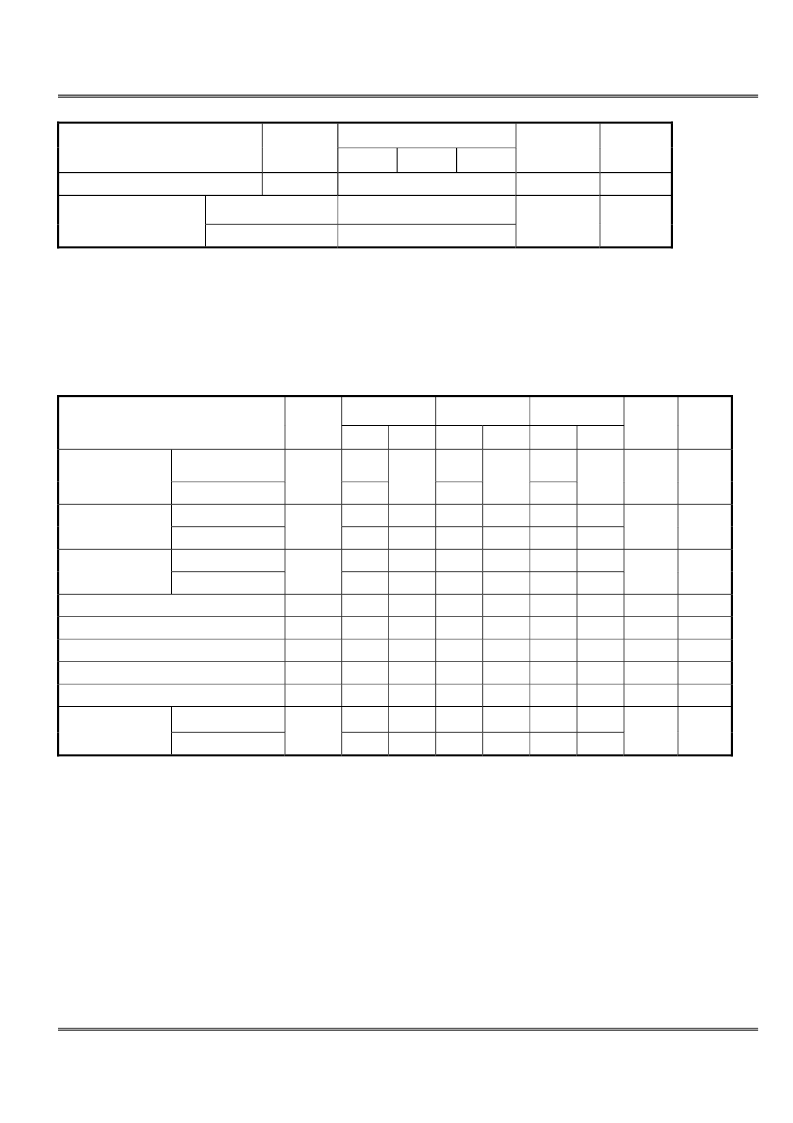

Parameter

Symbol

-5

-6

-7

Unit

Note

Col. address to col. address delay

t

CCD(min)

1

CLK

3

CAS latency = 3

2

Number of valid

Output data

CAS latency = 2

1

ea

4

Note : 1. The minimum number of clock cycles is determined by dividing the minimum time required with clock cycle time and then

rounding off to the next higher integer.

2. Minimum delay is required to complete write.

3. All parts allow every cycle column address change.

4. In case of row precharge interrupt, auto precharge and read burst stop.

AC CHARACTERISTICS

(AC operating condition unless otherwise noted)

-5

-6

-7

Parameter

Symbol

Min

Max

Min

Max

Min

Max

Unit

Note

CAS latency = 3

5

6

7

CLK cycle time

CAS latency = 2

t

CC

10

1000

10

1000

10

1000

ns

1

CAS latency = 3

4.5

5.5

6

CLK to valid

output delay

CAS latency = 2

t

SAC

10

6

6

ns

1,2

CAS latency = 3

2

2

2

Output data

hold time

CAS latency = 2

t

OH

2

2

2

ns

2

CLK high pulsh width

t

CH

2

2.5

2.5

ns

3

CLK low pulsh width

t

CL

2

2.5

2.5

ns

3

Input setup time

t

SS

1.5

1.5

2

ns

3

Input hold time

t

SH

1

1

1

ns

3

CLK to output in Low-Z

t

SLZ

1

1

1

ns

2

CAS latency = 3

4.5

5.5

6

CLK to output

in Hi-Z

CAS latency = 2

t

SHZ

6

6

6

ns

Note : 1. Parameters depend on programmed CAS latency.

2. If clock rising time is longer than 1ns. (tr/2 - 0.5) ns should be considered.

3. Assumed input rise and fall time (tr & tf) =1ns.

If tr & tf is longer than 1ns. transient time compensation should be considered.

i.e., [(tr + tf)/2 – 1] ns should be added to the parameter.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M12L64322A-7TG | 512K x 32 Bit x 4 Banks Synchronous DRAM |

| M12S128168A | 2M x 16 Bit x 4 Banks Synchronous DRAM |

| M12S128168A-10TG | 2M x 16 Bit x 4 Banks Synchronous DRAM |

| M12S16161A-7BG | 512K x 16Bit x 2Banks Synchronous DRAM |

| M12S16161A-7TG | 512K x 16Bit x 2Banks Synchronous DRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M12L64322A-7BG2U | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:512K x 32 Bit x 4 Banks |

| M12L64322A-7T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:512K x 32 Bit x 4 Banks Synchronous DRAM |

| M12L64322A-7TG | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:512K x 32 Bit x 4 Banks Synchronous DRAM |

| M12L64322A-7TG2U | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:512K x 32 Bit x 4 Banks |

| M-12-LID-PLATED | 功能描述:罩類、盒類及殼類產(chǎn)品 PLTD LID FOR M12 RoHS:否 制造商:Bud Industries 產(chǎn)品:Boxes 外部深度:6.35 mm 外部寬度:6.35 mm 外部高度:2.56 mm NEMA 額定值: IP 等級: 材料:Acrylonitrile Butadiene Styrene (ABS) 顏色:Red |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。