- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377801 > M12L64322A-7TG (ELITE SEMICONDUCTOR MEMORY TECHNOLOGY INC) 512K x 32 Bit x 4 Banks Synchronous DRAM PDF資料下載

參數(shù)資料

| 型號(hào): | M12L64322A-7TG |

| 廠商: | ELITE SEMICONDUCTOR MEMORY TECHNOLOGY INC |

| 元件分類: | DRAM |

| 英文描述: | 512K x 32 Bit x 4 Banks Synchronous DRAM |

| 中文描述: | 2M X 32 SYNCHRONOUS DRAM, 6 ns, PDSO86 |

| 封裝: | 0.400 X 0.875 INCH, 0.50 MM PITCH, LEAD FREE, TSOP2-86 |

| 文件頁(yè)數(shù): | 5/47頁(yè) |

| 文件大?。?/td> | 791K |

| 代理商: | M12L64322A-7TG |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)

ES MT

M12L64322A

Elite Semiconductor Memory Technology Inc.

Publication Date: Mar. 2007

Revision

:

2.3

5/47

PIN

NAME

INPUT FUNCTION

DQM0~3

Data Input / Output Mask

Makes data output Hi-Z, t

SHZ

after the clock and masks the output.

Blocks data input when DQM active.

DQ0 ~ DQ31

Data Input / Output

Data inputs / outputs are multiplexed on the same pins.

V

DD

/ V

SS

Power Supply / Ground

Power and ground for the input buffers and the core logic.

V

DDQ

/ V

SSQ

Data Output Power / Ground

Isolated power supply and ground for the output buffers to provide

improved noise immunity.

N.C

No Connection

This pin is recommended to be left No Connection on the device.

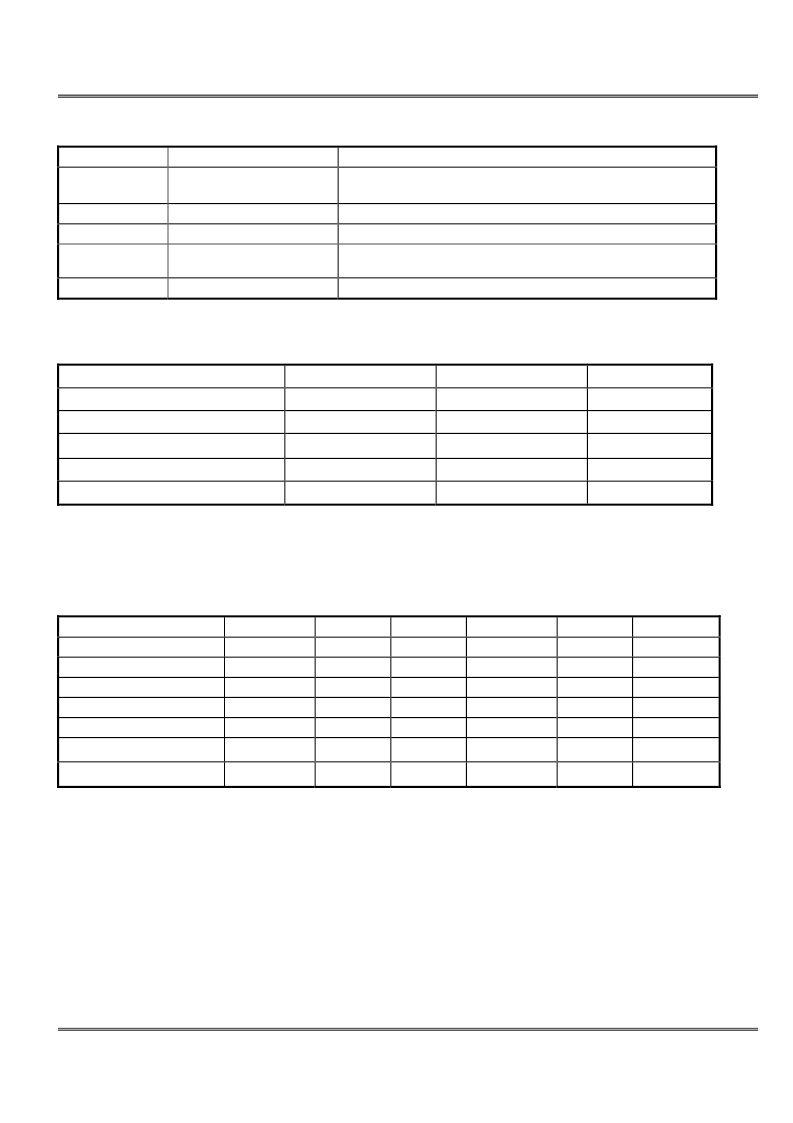

ABSOLUTE MAXIMUM RATINGS

Parameter

Symbol

Value

Unit

Voltage on any pin relative to V

SS

V

IN

, V

OUT

-1.0 ~ 4.6

V

Voltage on V

DD

supply relative to V

SS

V

DD

, V

DDQ

-1.0 ~ 4.6

V

Storage temperature

T

STG

-55 ~ +150

C

°

Power dissipation

P

D

1

W

Short circuit current

Note :

Permanent device damage may occur if ABSOLUTE MAXIMUM RATING are exceeded.

Functional operation should be restricted to recommended operating condition.

Exposure to higher than recommended voltage for extended periods of time could affect device reliability.

DC OPERATING CONDITION

Recommended operating conditions (Voltage referenced to V

SS

= 0V, T

A

= 0 to 70° )

I

OS

50

mA

Parameter

Symbol

Min

Typ

Max

Unit

Note

Supply voltage

V

DD

, V

DDQ

3.0

3.3

3.6

V

Input logic high voltage

V

IH

2.0

3.0

V

DD

+0.3

V

1

Input logic low voltage

V

IL

-0.3

0

0.8

V

2

Output logic high voltage

V

OH

2.4

-

-

V

I

OH

= -2mA

Output logic low voltage

V

OL

-

-

0.4

V

μ

A

I

OL

= 2mA

Input leakage current

I

IL

-5

-

5

3

Output leakage current

I

OL

-5

-

5

μ

A

4

Note:

1. V

IH

(max) = 4.6V AC for pulse width

≤

4. Dout is disabled , 0V

≤

V

OUT

≤

V

DD

.

2. V

IL

(min) = -1.5V AC for pulse width

≤

10ns acceptable.

3. Any input 0V

≤

VIN

≤

V

DD

+ 0.3V, all other pins are not under test = 0V.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M12S128168A | 2M x 16 Bit x 4 Banks Synchronous DRAM |

| M12S128168A-10TG | 2M x 16 Bit x 4 Banks Synchronous DRAM |

| M12S16161A-7BG | 512K x 16Bit x 2Banks Synchronous DRAM |

| M12S16161A-7TG | 512K x 16Bit x 2Banks Synchronous DRAM |

| M12S64322A | 512K x 32 Bit x 4 Banks Synchronous DRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M12L64322A-7TG2U | 制造商:ESMT 制造商全稱:Elite Semiconductor Memory Technology Inc. 功能描述:512K x 32 Bit x 4 Banks |

| M-12-LID-PLATED | 功能描述:罩類、盒類及殼類產(chǎn)品 PLTD LID FOR M12 RoHS:否 制造商:Bud Industries 產(chǎn)品:Boxes 外部深度:6.35 mm 外部寬度:6.35 mm 外部高度:2.56 mm NEMA 額定值: IP 等級(jí): 材料:Acrylonitrile Butadiene Styrene (ABS) 顏色:Red |

| M12M1 | 制造商:TE Connectivity 功能描述: |

| M12M124D-0.5 | 制造商:L COM 功能描述:CA M12 TO M12 4 POS D .5M |

| M12M124D-1 | 制造商:L COM 功能描述:CA M12 TO M12 4 POS D 1M |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。