- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45048 > M38C59GFHP 8-BIT, OTPROM, 6.25 MHz, MICROCONTROLLER, PQFP80 PDF資料下載

參數(shù)資料

| 型號(hào): | M38C59GFHP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, OTPROM, 6.25 MHz, MICROCONTROLLER, PQFP80 |

| 封裝: | 12 X 12 MM, 0.50 MM PITCH, PLASTIC, LQFP-80 |

| 文件頁數(shù): | 21/71頁 |

| 文件大小: | 939K |

| 代理商: | M38C59GFHP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當(dāng)前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁

Rev.2.00

Nov 23, 2005

page 28 of 75

REJ03B0098-0200

38C5 Group (One Time PROM version)

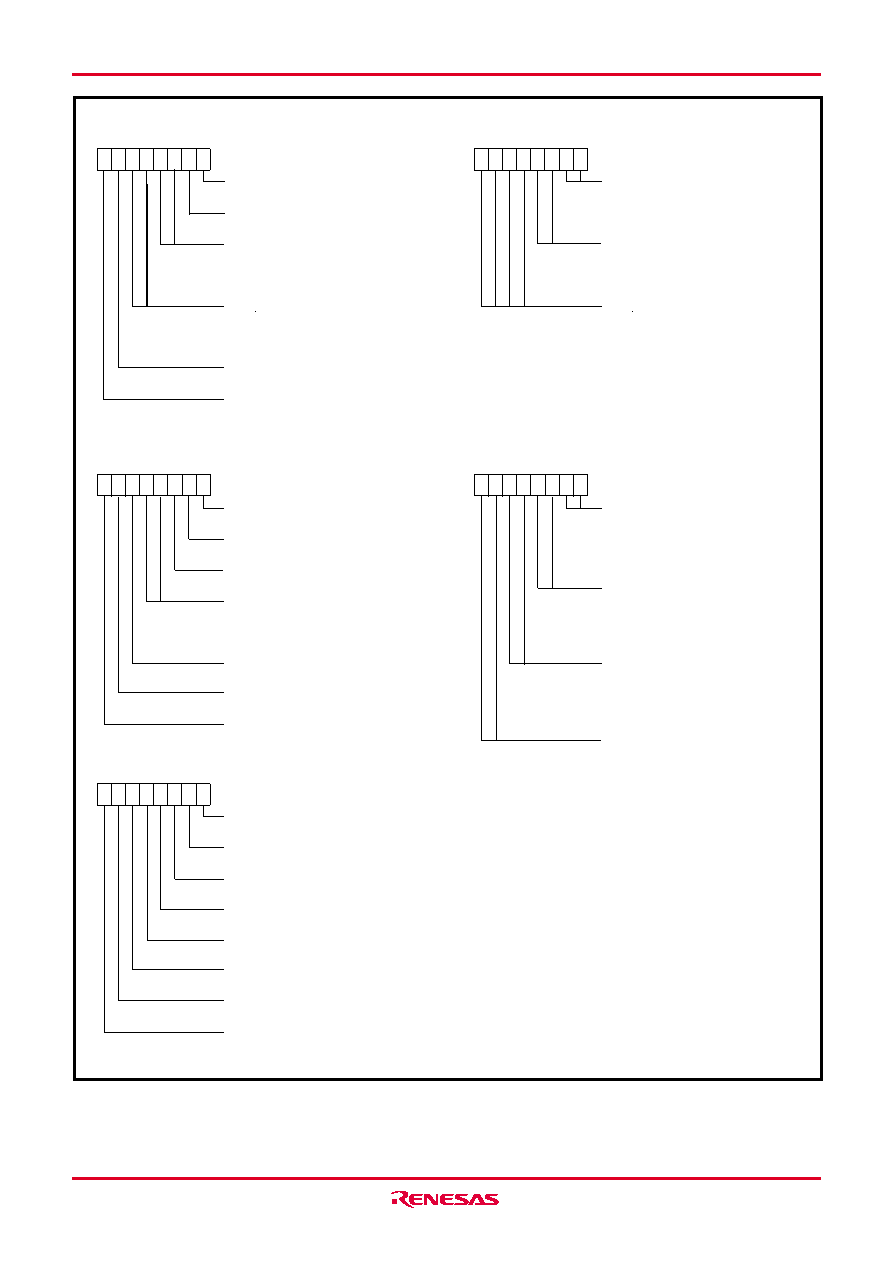

Fig. 24 Structure of Timer 1 to timer 4 related registers

Timer 12 mode register

(T12M: address 002516)

Timer 1 count stop bit

0 : Count operation

1 : Count stop

Timer 2 count stop bit

0 : Count operation

1 : Count stop

Timer 1 count source selection bits

b3 b2

00 : Frequency divider for Timer 1

01 : f(XCIN)

10 : Underflow of Timer Y

11 : Not available

Timer 2 count source selection bits

b5 b4

00 : Underflow of Timer 1

01 : f(XCIN)

10 : Frequency divider for Timer 2

11 : Not available

Timer 2 output selection bit (P72)

0 : I/O port

1 : Timer 2 output

T2OUT output edge switch bit

0 : Start at “L” output

1 : Start at “H” output

Timer 34 mode register

(T34M: address 002616)

Timer 3 count stop bit

0 : Count operation

1 : Count stop

Timer 4 count stop bit

0 : Count operation

1 : Count stop

Timer 3 count source selection bit

0 : Frequency divider for Timer 3

1 : Underflow of Timer 2

Timer 4 count source selection bits

b4 b3

0 0 : Frequency divider for Timer 4

0 1 : Underflow of Timer 3

1 0 : Underflow of Timer 2

1 1 : f(XIN)

Timer 3 operating mode selection bit

0 : Timer mode

1 : PWM mode

Timer 4 operating mode selection bit

0 : Timer mode

1 : PWM mode

Not used (returns “0” when read)

Timer 1234 mode register

(T1234M: address 002716)

T3OUT output edge switch bit

0 : Start at “L” output

1 : Start at “H” output

T4OUT output edge switch bit

0 : Start at “L” output

1 : Start at “H” output

Timer 3 output selection bit (P73)

0 : I/O port

1 : Timer 3 output

Timer 4 output selection bit (P74)

0 : I/O port

1 : Timer 4 output

Timer 2 write control bit

0 : Write data to both timer latch and timer

1 : Write data to timer latch only

Timer 3 write control bit

0 : Write data to both timer latch and timer

1 : Write data to timer latch only

Timer 4 write control bit

0 : Write data to both timer latch and timer

1 : Write data to timer latch only

Not used (returns “0” when read)

b7

b0

b7

b0

b7

b0

PWM01 register

(PWM01: address 002416)

PWM0 set bits

b1 b0

00 : No extended

01 : Extended once in four periods

10 : Extended twice in four periods

11 : Extended three times in four periods

PWM1 set bits

b3 b2

00 : No extended

01 : Extended once in four periods

10 : Extended twice in four periods

11 : Extended three times in four periods

Not used (returns “0” when read)

Timer 1234 frequency division selection register

(PRE1234: address 002816)

Timer 1 frequency division selection bits

b1 b0

0 0 : 1/16

φ SOURCE

0 1 : 1/1

φ SOURCE

1 0 : 1/2

φ SOURCE

1 1 : 1/256

φ SOURCE

Timer 2 frequency division selection bits

b3 b2

0 0 : 1/16

φ SOURCE

0 1 : 1/1

φ SOURCE

1 0 : 1/2

φ SOURCE

1 1 : 1/256

φ SOURCE

Timer 3 frequency division selection bits

b5 b4

0 0 : 1/16

φ SOURCE

0 1 : 1/1

φ SOURCE

1 0 : 1/2

φ SOURCE

1 1 : 1/256

φ SOURCE

Timer 4 frequency division selection bits

b7 b6

0 0 : 1/16

φ SOURCE

0 1 : 1/1

φ SOURCE

1 0 : 1/2

φ SOURCE

1 1 : 1/256

φ SOURCE

b7

b0

b7

b0

φ SOURCE: represents the oscillation frequency of

XIN input in the middle- and high-speed mode,

on-chip oscillator divided by 4 in the on-chip

oscillator mode,

and sub-clock in the low-speed mode.

Note:

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M38C89EFFP | 8-BIT, OTPROM, 4 MHz, MICROCONTROLLER, PQFP144 |

| M38C89MF-XXXFP | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQFP144 |

| M38C89EFFP | 8-BIT, OTPROM, 4 MHz, MICROCONTROLLER, PQFP144 |

| M38C89MF-XXXFP | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQFP144 |

| M38C89EFFP | 8-BIT, OTPROM, 4 MHz, MICROCONTROLLER, PQFP144 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M38C59GFHP#U0 | 制造商:Renesas Electronics Corporation 功能描述:MCU 2/4V 60K PB-FREE - Trays |

| M38D20F1XXXFP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38D20F1XXXHP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38D20F2XXXFP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38D20F2XXXHP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。