- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370992 > M66271FP (Mitsubishi Electric Corporation) OPERATION PANEL CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | M66271FP |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | OPERATION PANEL CONTROLLER |

| 中文描述: | 操作面板控制器 |

| 文件頁數(shù): | 6/21頁 |

| 文件大小: | 289K |

| 代理商: | M66271FP |

OPERATION PANEL CONTROLLER

M66271FP

MITSUBISHI <DIGITAL ASSP>

Function of cycle steal control

M66271FP has a function for processing data of a line with

more efficient. This function access with the cycle steal

method as taking WAIT for MPU during the display term

with necessity for the display data transfer from built-in

VRAM to LCD.

On other side, don't output WAIT for keeping throughput of

Ex.) Assuming 320

×

240 dots LCD

UD<3:0>

4bit transfer

LP

Output when finish transfer

of display data with a line

CP

Output every transfer of

a display data

Displaying term (Cycle steal method)

(Necessity for data transfer from VRAM to LCD side)

Horizontal synchronous term

(No necessity for data transfer from VRAM to LCD side)

CSE

(Internal signal)

Start WAIT for MPU according to

cycle steal access.

Access with bus timing of MPU

without WAIT for MPU.

Start WAIT for MPU in timing of CSE "H"

according to bus timing of MPU.

Setting by CR register

1 Line

Setting by LPW register

1

2

3

1

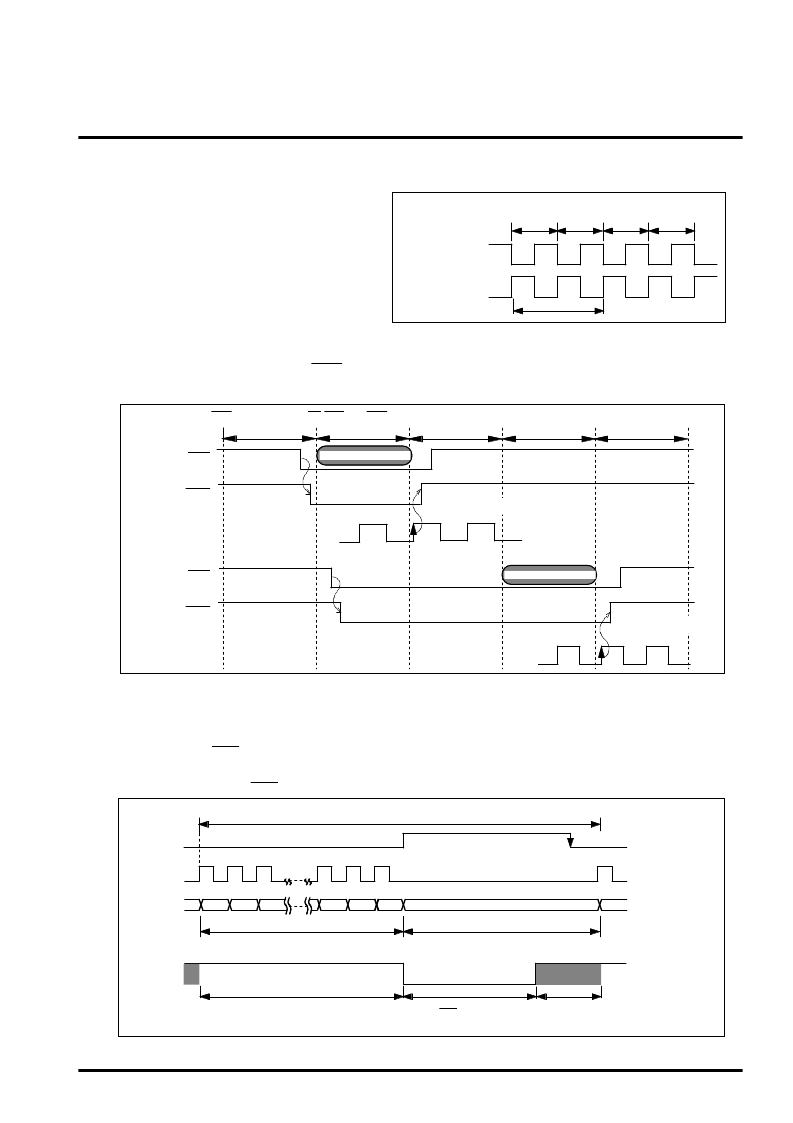

Basic timing of M66271FP is two clocks of OSC

(internal clock after dividing OSC1 input).

Assign first clock to accessing from MPU to VRAM

and second clock to transferring of display data

from VRAM to LCD

BASIC TIMING

Description of cycle steal

Figure-2 BASIC TIMING

OSC

(Internal clock after

dividing OSC1 input)

CP output

(Display data transfer)

Data transfer

from VRAM

to LCD

Access

from MPU

to VRAM

LCD

MPU

Basic cycle

Writing or Reading operation for VRAM during cycle steal

needs 1 cycle in best case or 3 cycles in worst case,

Cycle of

LCD access

Cycle of

MPU access

Worst case

Best case

Cycle of

LCD access

Cycle of

MPU access

Cycle of

LCD access

Operation cycle of MPU access(during WAIT output)

MCS

WAIT

MCS

WAIT

Figure-3 Operation cycle of MPU access

MPUCLK

MPUCLK

Operation cycle ofMPU access

according to the condition of the internal cycle steal at staring

access requested from MPU.

Ex.) Assuming that MCS input is later than RD,LWR and HWR input.

Cancel WAIT,when synchronize

with rising edge of MPUCLK

Cancel WAIT,when synchronize

with rising edge of MPUCLK

MPU during the horizontal synchronous term with no necessity

for the display data transfer from VRAM to LCD side.

But certainly set a term of accessing with the cycle steal

method by CSW register, for controlling an error action near

the end of horizontal synchronous term.

Setting by CSW register

Figure-4 Function of cycle steal control

Operation cycle ofMPU access

78

79

80

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M66272 | LCD CONTROLLER with VRAM |

| M66272FP | LCD CONTROLLER with VRAM |

| M66287FP | 262144-word x 8-bit x 3-FIELD MEMORY |

| M66307FP | LINE SCAN BUFFER with 16-BIT MPU BUS COMPATIBLE INPUTS |

| M66307SP | LINE SCAN BUFFER with 16-BIT MPU BUS COMPATIBLE INPUTS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M66272 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:LCD CONTROLLER with VRAM |

| M66272FP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:LCD CONTROLLER with VRAM |

| M66273FP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:LCD CONTROLLER with VRAM |

| M66280FP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:5120 x 8-BIT LINE MEMORY |

| M66280FP(#TB0T) | 制造商:Renesas Electronics Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。