- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359141 > MC68HC08JK3EMDW (飛思卡爾半導(dǎo)體(中國(guó))有限公司) Microcontrollers PDF資料下載

參數(shù)資料

| 型號(hào): | MC68HC08JK3EMDW |

| 廠商: | 飛思卡爾半導(dǎo)體(中國(guó))有限公司 |

| 英文描述: | Microcontrollers |

| 中文描述: | 微控制器 |

| 文件頁(yè)數(shù): | 111/180頁(yè) |

| 文件大?。?/td> | 1018K |

| 代理商: | MC68HC08JK3EMDW |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)當(dāng)前第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)

Port D

MC68HC908JL3E Family Data Sheet, Rev. 4

Freescale Semiconductor

111

10.4.2 Data Direction Register D (DDRD)

Data direction register D determines whether each port D pin is an input or an output. Writing a one to a

DDRD bit enables the output buffer for the corresponding port D pin; a zero disables the output buffer.

DDRD[7:0] — Data Direction Register D Bits

These read/write bits control port D data direction. Reset clears DDRD[7:0], configuring all port D pins

as inputs.

1 = Corresponding port D pin configured as output

0 = Corresponding port D pin configured as input

NOTE

Avoid glitches on port D pins by writing to the port D data register before

changing data direction register D bits from 0 to 1.

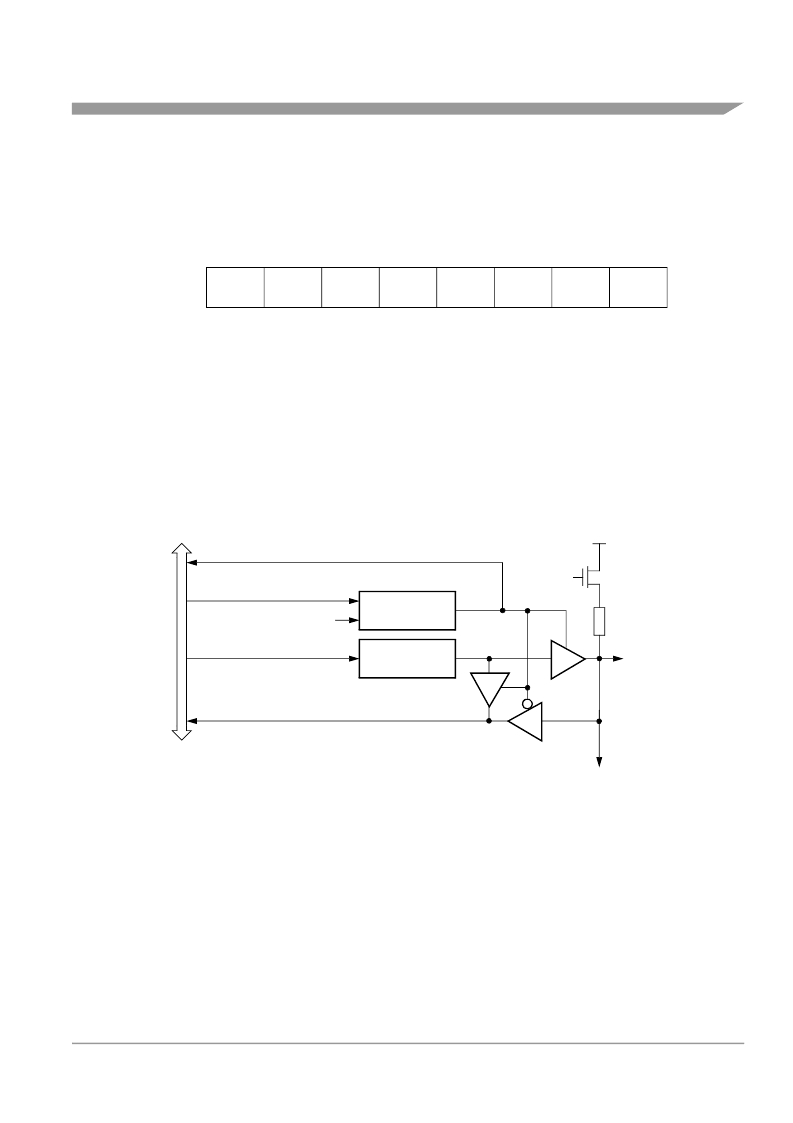

Figure 10-11

shows the

port D I/O logic.

Figure 10-11. Port D I/O Circuit

When DDRDx is a 1, reading address $0003 reads the PTDx data latch. When DDRDx is a 0, reading

address $0003 reads the voltage level on the pin. The data latch can always be written, regardless of the

state of its data direction bit.

Table 10-4

summarizes the operation of the port D pins.

Address:

$0007

Bit 7

6

5

4

3

2

1

Bit 0

Read:

DDRD7

DDRD6

DDRD5

DDRD4

DDRD3

DDRD2

DDRD1

DDRD0

Write:

Reset:

0

0

0

0

0

0

0

0

Figure 10-10. Data Direction Register D (DDRD)

READ DDRD ($0007)

WRITE DDRD ($0007)

RESET

WRITE PTD ($0003)

READ PTD ($0003)

PTDx

DDRDx

PTDx

I

PTD[0:3] To Analog-To-Digital Converter

PTD[4:5] To Timer

5k

PTDPU[6:7]

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC68HC08JK8CDW | Microcontrollers |

| MC68HC08JL3H | Microcontrollers |

| MC68HC08JT8 | M68HC08 Microcontrollers |

| MC68HC08KH12A | Microcontrollers |

| MC68HC08LT8 | Microcontrollers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC68HC08JK3EMP | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontrollers |

| MC68HC08JK8 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontrollers |

| MC68HC08JK8CDW | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontrollers |

| MC68HC08JK8CP | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Addendum to MC68HC908JL8 Technical Data |

| MC68HC08JK8MDW | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Microcontrollers |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。