- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98045 > MT8LLN22NCNE PCI BUS CONTROLLER, PBGA316 PDF資料下載

參數(shù)資料

| 型號: | MT8LLN22NCNE |

| 元件分類: | 總線控制器 |

| 英文描述: | PCI BUS CONTROLLER, PBGA316 |

| 封裝: | 27 X 27 MM, PLASTIC, BGA-316 |

| 文件頁數(shù): | 24/145頁 |

| 文件大小: | 2285K |

| 代理商: | MT8LLN22NCNE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁

Coppertail Product Specification

MT8LLN22NCNE.fm – Rev. 1, Pub. 2/02

12

2002, Micron Technology Inc.

PRELIMINARY

MT8LLN22NCNE

COPPERTAIL

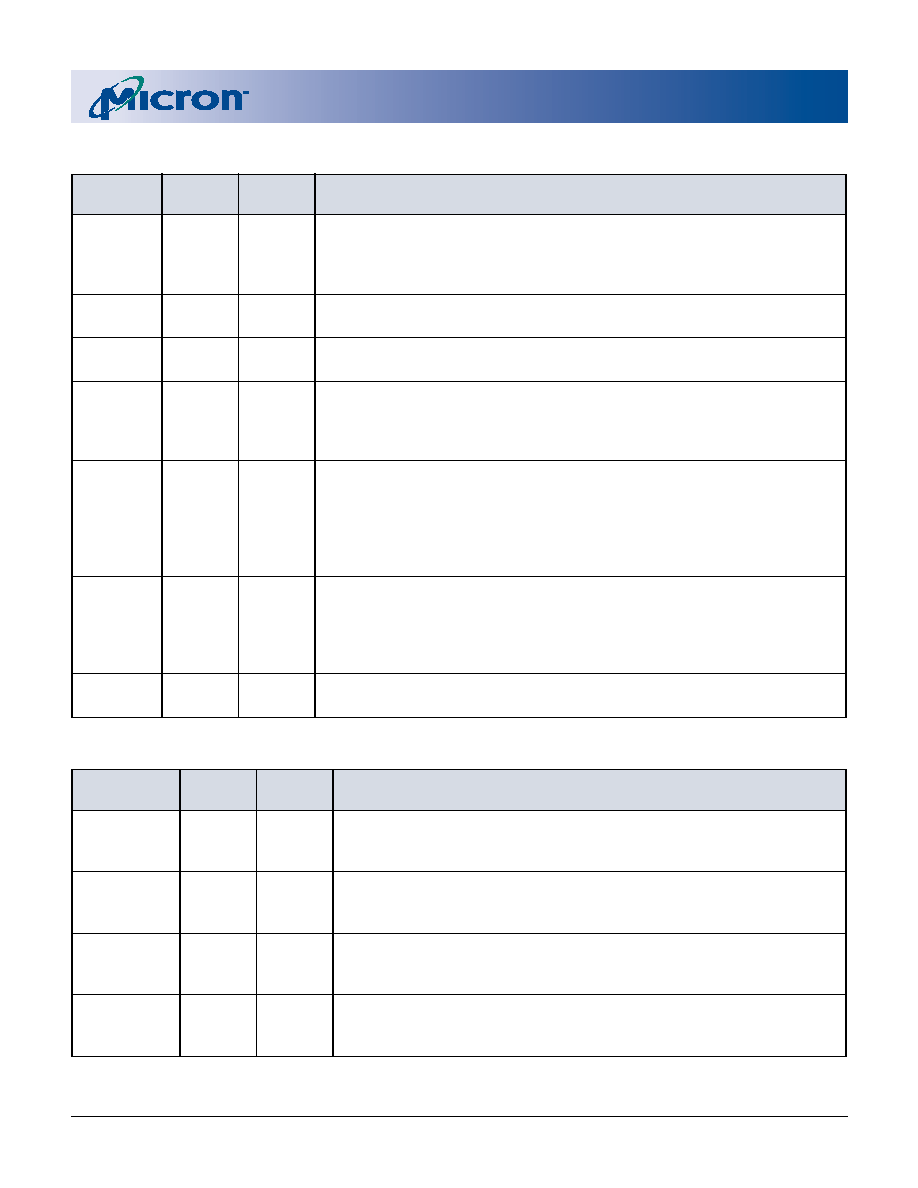

P_PERR#

I

VDD3.3

Parity Error. P_PERR# is used for reporting data parity errors during all PCI

transactions except a special cycle. An external PCI device drives PERR#

when it receives data that has a parity error. The I/O Controller can either

generate a NMI# or SMI# upon detecting a parity error.

P_REQ_1#

0

VDD3.3

PCI Request 1. An active low assertion indicates that the I/O Controller

desires use of the PCI bus. Primary arbitration request

P_REQ_2#

O

VDD3.3

PCI Request 2. Optional dedicated PCI request for internal IDE and USB,

with P_REQ_1# dedicated to the LPC bridge. Secondary arbitration request

P_REQ#

[4:0]

IVDD3.3

PCI Request. P_REQ#[4:0] signals are used by PCI devices to request access

to the PCI bus. The power management unit monitors these inputs with

the internal PCI masters in order to wake the CPU in the case of master

attempting a bus master cycle while the CPU is in a Sleep state.

P_SERR#

I

VDD3.3

PCI System Error. P_SERR# is used for reporting address parity errors, data

parity errors on the special cycle command, or any other system error

where the result will be catastrophic. P_SERR# can be pulsed active by any

PCI device that detects a system error condition. Upon sampling SERR#

active, the I/O Controller has the ability to generate a NMI#, SMI#, or SCI

interrupt.

P_STOP#

I/O

VDD3.3

PCI Stop. P_STOP# indicates that the I/O Controller, as a target, is request-

ing the initiator to stop the current transaction. P_STOP# causes the I/O

Controller, as an initiator, to stop the current transaction. P_STOP# is an

output when the I/O Controller is a target and an input when the I/O Con-

troller is an initiator.

P_TRDY#

I/O

VDD3.3

PCI Target Ready. Output when the I/O controller functions as a target and

input when I/O controller functions as the initiator.

PCI Signal Descriptions (continued)

SIGNAL

TYPE

POWER

PLANE

DESCRIPTION

USB Interface

SIGNAL

TYPE

POWER

PLANE

DESCRIPTION

USB_DATA1P

USB_DATA1N

USB I/O

Standby

USB Port 1. Differential signals used to transmit USB data, address, and

command. Supports both full speed (12Mb) and low speed (1.5Mb) data

rates. Powered off of the standby plane.

USB_DATA2P

USB_DATA2N

USB I/O

Standby

USB Port 2. Differential signals used to transmit USB data, address, and

command. Supports both full speed (12Mb) and low speed (1.5Mb) data

rates. Powered off of the standby plane.

USB_DATA3P

USB_DATA3N

USB I/O

Standby

USB Port 3. Differential signals used to transmit USB data, address, and

command. Supports both full speed (12Mb) and low speed (1.5Mb) data

rates. Powered off of the standby plane.

USB_DATA4P

USB_DATA4N

USB I/O

Standby

USB Port 4. Differential signals used to transmit USB data, address, and

command. Supports both full speed (12Mb) and low speed (1.5Mb) data

rates. Powered off of the standby plane.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MTB10N40ET4 | 10 A, 400 V, 0.55 ohm, N-CHANNEL, Si, POWER, MOSFET |

| MTB15N06V | 15 A, 60 V, 0.12 ohm, N-CHANNEL, Si, POWER, MOSFET |

| MTB15N06VT4 | 15 A, 60 V, 0.12 ohm, N-CHANNEL, Si, POWER, MOSFET |

| MTB16N25E | 16 A, 250 V, 0.25 ohm, N-CHANNEL, Si, POWER, MOSFET |

| MTB16N25ET4 | 16 A, 250 V, 0.25 ohm, N-CHANNEL, Si, POWER, MOSFET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT8LLN22NCNE-A | 制造商:Micron Technology Inc 功能描述:COPPERTAIL CHIPSET - Trays |

| MT8LLN22NCNE-A2 | 制造商:Micron Technology Inc 功能描述:COPPERTAIL CHIPSET AND MOTHERBOARD - Trays |

| MT8LSDF3264WG-133D1 | 制造商:Micron Technology Inc 功能描述:256MB 32MX64 SYNCH DRAM MODULE MICRO DIMM 3.3V - Trays |

| MT8LSDT1664 | 制造商:Micron Technology Inc 功能描述:128MB 16MX64 SDRAM MODULE PBF DIMM 3.3V - Trays |

| MT8LSDT1664AG-10EB1 | 制造商:Micron Technology Inc 功能描述:DRAM MOD SDRAM 1GBIT 168UDIMM - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。