- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98045 > MT8LLN22NCNE PCI BUS CONTROLLER, PBGA316 PDF資料下載

參數(shù)資料

| 型號(hào): | MT8LLN22NCNE |

| 元件分類: | 總線控制器 |

| 英文描述: | PCI BUS CONTROLLER, PBGA316 |

| 封裝: | 27 X 27 MM, PLASTIC, BGA-316 |

| 文件頁數(shù): | 78/145頁 |

| 文件大小: | 2285K |

| 代理商: | MT8LLN22NCNE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁當(dāng)前第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁

Coppertail Product Specification

MT8LLN22NCNE.fm – Rev. 1, Pub. 2/02

38

2002, Micron Technology Inc.

PRELIMINARY

MT8LLN22NCNE

COPPERTAIL

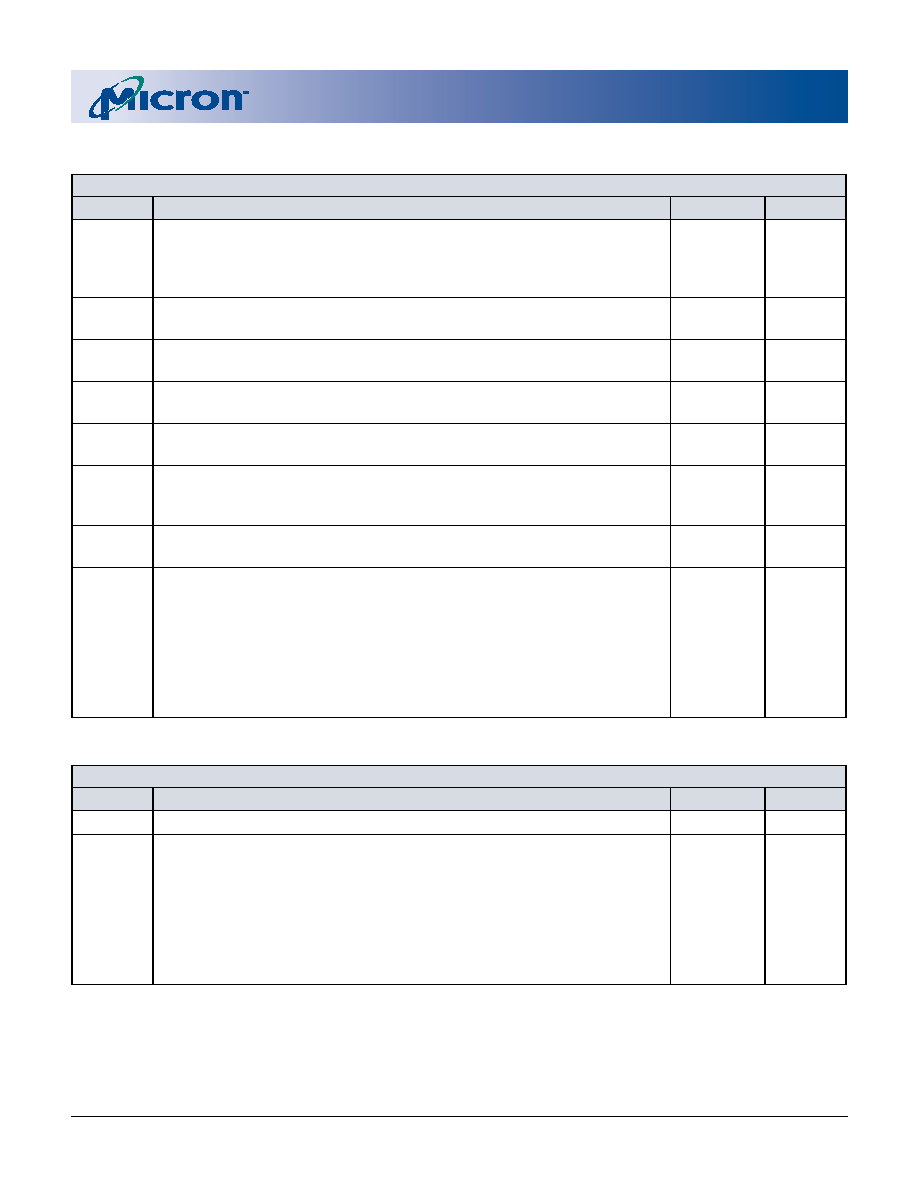

Extended I/O APIC Control (Device 7h, Function 0h)

ADDRESS: A1h

SYMBOL: IOAPIC

BITS

DESCRIPTION

PROPERTIES

RESET

7

Enable expanded PCI Interrupt (P_INT[15:0]) routing to 8259’s. When set,

P_INT[15:0] will be routed to the 8259’s based on their corresponding

interrupt routing register. When clear, P_INT[15:0] will be routed to the

8259’s based on P_INT[D:A] routing.

R/W

0

6

Retry acceptance exception. When set, retry for Status A1 will cause the

Arbitration ID to increment

R/W

0

5

Status A1 increment exception. When set, Status A1 will cause the arbiter

to increment to the next interrupt to be delivered.

R/W

0

4

Lowest priority zeros accepted. When set a Status A1 of zeros will be

used as an acceptance for lowest priority interrupts.

R/W

0

3

Deassert message enable. When set, deassert messages will be transmit-

ted on the APIC bus.

R/W

0

2

PCI Message signaled interrupt EOI support enable. When set writes to

the IRQ pin assertion register will cause interrupt delivery status to be

set.

R/W

0

1

PCI Message signaled interrupt request support enable. When set writes

to the EOI assertion register will cause Remote IRR status to clear.

R/W

0

Expanded I/O APIC Disable. When set, the I/O supports the standard 24

interrupt inputs. When clear, the I/O APIC supports the expanded 40

interrupt inputs.

P_INT[15:0] are connected internally to P_INT[D:A] as follows:

P_INT[0,4,8,12] to P_INT[A].

P_INT[1,5,9,13] to P_INT[B].

P_INT[2,6,10,14] to P_INT[C].

P_INT[3,7,11,15] to P_INT[D].

R/W

0

Extended Trap Control (Device 7h, Function 0h)

ADDRESS: A2h

SYMBOL: EXT_TRAP

BITS

DESCRIPTION

PROPERTIES

RESET

7:4

Reserved

R/W

0

3

GPA1R. Capture writes enable. When set, the south bridge will observe

the address, data, byte enables, and command for a write transaction

that falls into the General Purpose Trap Address 1 (GPTA1) and store

them in TRAP_ADDR, TRAP_DATA, and TRAP_CMND. The address, status,

and space type is defined in GPAR1. The address bits to be masked as

part of the trap are defined in DEVCTL. The trap will be performed inde-

pendent of whether SMI traps are enabled in general or if the SMI trap is

enabled for GPTA1.

R/W

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MTB10N40ET4 | 10 A, 400 V, 0.55 ohm, N-CHANNEL, Si, POWER, MOSFET |

| MTB15N06V | 15 A, 60 V, 0.12 ohm, N-CHANNEL, Si, POWER, MOSFET |

| MTB15N06VT4 | 15 A, 60 V, 0.12 ohm, N-CHANNEL, Si, POWER, MOSFET |

| MTB16N25E | 16 A, 250 V, 0.25 ohm, N-CHANNEL, Si, POWER, MOSFET |

| MTB16N25ET4 | 16 A, 250 V, 0.25 ohm, N-CHANNEL, Si, POWER, MOSFET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT8LLN22NCNE-A | 制造商:Micron Technology Inc 功能描述:COPPERTAIL CHIPSET - Trays |

| MT8LLN22NCNE-A2 | 制造商:Micron Technology Inc 功能描述:COPPERTAIL CHIPSET AND MOTHERBOARD - Trays |

| MT8LSDF3264WG-133D1 | 制造商:Micron Technology Inc 功能描述:256MB 32MX64 SYNCH DRAM MODULE MICRO DIMM 3.3V - Trays |

| MT8LSDT1664 | 制造商:Micron Technology Inc 功能描述:128MB 16MX64 SDRAM MODULE PBF DIMM 3.3V - Trays |

| MT8LSDT1664AG-10EB1 | 制造商:Micron Technology Inc 功能描述:DRAM MOD SDRAM 1GBIT 168UDIMM - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。