- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383645 > MT9076AB (Mitel Networks Corporation) T1/E1/J1 3.3V Single Chip Transceiver PDF資料下載

參數(shù)資料

| 型號: | MT9076AB |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | T1/E1/J1 3.3V Single Chip Transceiver |

| 中文描述: | T1/E1/J1收發(fā)3.3V的單芯片收發(fā)器 |

| 文件頁數(shù): | 77/160頁 |

| 文件大小: | 416K |

| 代理商: | MT9076AB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁當(dāng)前第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁

Preliminary Information

MT9076

73

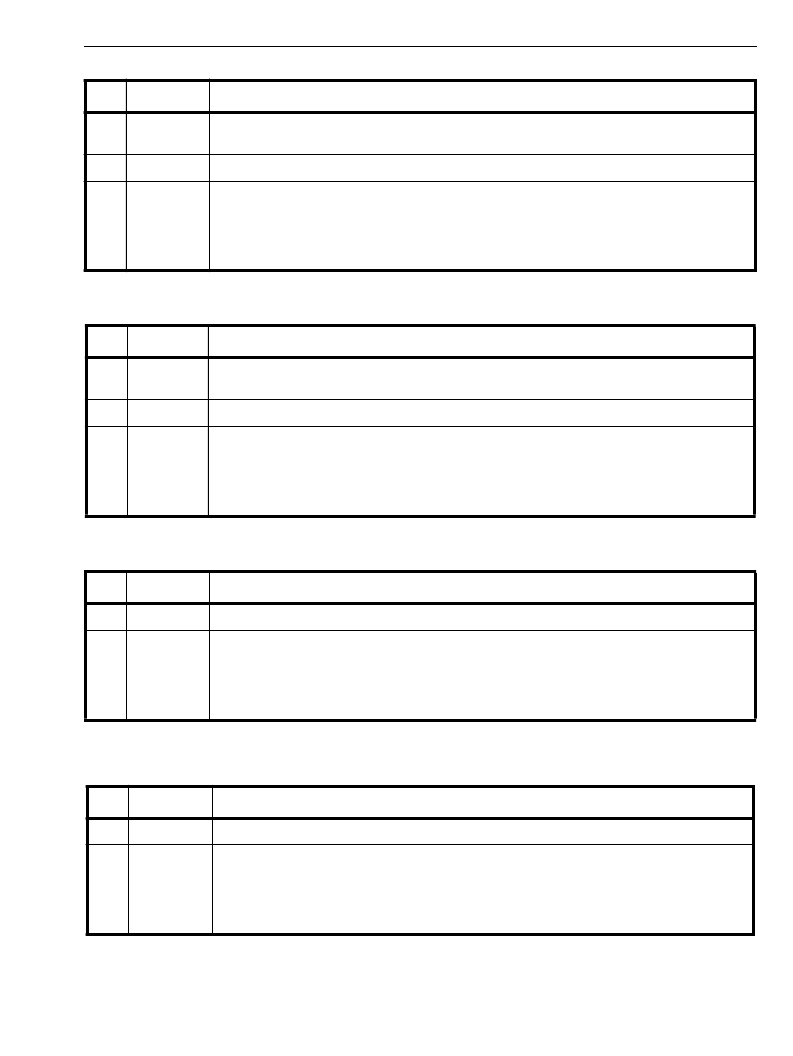

Bit

Name

Functional Description

7

En

Enable.

Set high to attach the HDLC1 controller to the channel specified below. Set low to

disconnect the HDLC1.

6-5

--

Reserved.

Must be kept at 0 for normal operation.

4-0

CH4-0

Channel 4-0.

This 5 bit number specifies the channel time HDLC1 will be attached to if

enabled. Channel 0 is the first channel in the frame. Channel 23 is the last channel available

in a T1 frame. If enabled in a channel, HDLC data will be substituted for data from DSTi on

the transmit side. Receive data is extracted from the incoming line data before the elastic

buffer.

Table 44 - HDLC1 Select

(Page 2, Address 1AH) (T1)

Bit

Name

Functional Description

7

En

Enable.

Set high to attach the HDLC2 controller to the channel specified below. Set low to

disconnect the HDLC2.

6-5

- -

Reserved.

Must be kept at 0 for normal operation.

4-0

CH4-0

Channel 4-0.

This 5 bit number specifies the channel time HDLC2 will be attached to if

enabled. Channel 0 is the first channel in the frame. Channel 23 is the last channel available

in a T1 frame. If enabled in a channel, HDLC data will be substituted for data from DSTi on

the transmit side. Receive data is extracted from the incoming line data before the elastic

buffer.

Table 45 - HDLC2 Select

(Page 2, Address 1BH) (T1)

Bit

Name

Functional Description

7

- -

Reserved.

Must be kept at 0 for normal operation.

6-0

CP6-0

Custom Pulse.

These bits provide the capability for programming the magnitude setting for

the TTIP/TRING line driver A/D converter during the first phase of a mark. The greater the

binary number loaded into the register, the greater the amplitude driven out. This feature is

enabled when the control bit 3 - CPL of the Custom Tx Pulse Enable Register - address 11H

of Page 2 is set high.

Table 46 - Custom Pulse Word 1

(Page 2, Address 1CH) (T1)

Bit

Name

Functional Description

7

-

Reserved.

Must be kept at 0 for normal operation.

6-0

CP6-0

Custom Pulse.

These bits provide the capability for programming the magnitude setting for

the TTIP/TRING line driver A/D converter during the second phase of a mark. The greater

the binary number loaded into the register, the greater the amplitude driven out. This

feature is enabled when the control bit 3 - CPL of the Custom Tx Pulse Enable Register -

address 11H of Page 2 is set high.

Table 47 - Custom Pulse Word 2

(Page 2, Address 1DH) (T1)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT9076 | T1/E1/J1 3.3V Single Chip Transceiver(T1/E1/J1 3.3V 單片收發(fā)器) |

| MT9079 | Advanced Controller for E1(先進(jìn)的E1幀調(diào)節(jié)器和控制器) |

| MT9080B | SMX - Switch Matrix Module(用于消費(fèi)類轉(zhuǎn)換應(yīng)用的開關(guān)矩陣模塊) |

| MT90810 | Flexible MVIP(Multi-Vendor Integration Protocol) Interface Circuit(彈性MVIP接口電路) |

| MT90812 | Integrated Digital Switch (IDX)(集成數(shù)字開關(guān)) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT9076AP | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:T1/E1/J1 3.3V Single Chip Transceiver |

| MT9076B | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:T1/E1/J1 3.3 V Single Chip Transceiver |

| MT9076BB | 制造商:Zarlink Semiconductor Inc 功能描述:FRAMER E1/J1/T1 3.3V 80LQFP - Trays |

| MT9076BB1 | 制造商:Zarlink Semiconductor Inc 功能描述:FRAMER E1/J1/T1 3.3V 80LQFP - Trays |

| MT9076BP | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:T1/E1/J1 3.3 V Single Chip Transceiver |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。