- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383645 > MT90810 (Mitel Networks Corporation) Flexible MVIP(Multi-Vendor Integration Protocol) Interface Circuit(彈性MVIP接口電路) PDF資料下載

參數(shù)資料

| 型號: | MT90810 |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | Flexible MVIP(Multi-Vendor Integration Protocol) Interface Circuit(彈性MVIP接口電路) |

| 中文描述: | 柔性MVIP(多廠商集成協(xié)議)接口電路(彈性MVIP接口電路) |

| 文件頁數(shù): | 17/33頁 |

| 文件大小: | 176K |

| 代理商: | MT90810 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁

Preliminary Information

MT90810

2-185

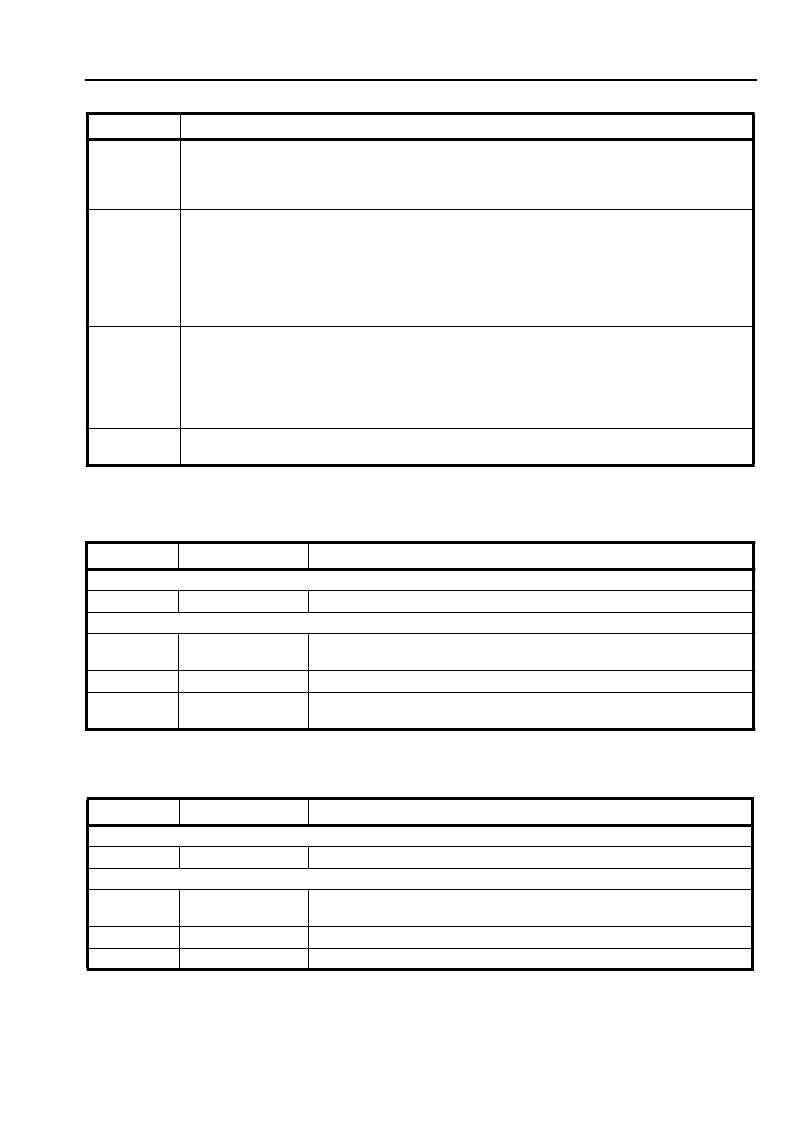

Notes: FRMx represents either FRMA for frame group A, or FRMB for group B

Mode [bits]

Description

0 [00]

Programmed output

FGx[0:11] are programmable output pins. All 8 bits of FRMx_START register are driven out

pins FGx[0:7] (with bit 0 corresponding to pin FGx[0] etc.) and bits 0-3 of FRMx_MODE register

are driven out pin FGx[8:11] (with bit 0 corresponding to pin FGx[8] etc.).

DSi/DSo output enables

FGA[4:11] pins correspond to output drive enables for the MVIP DSo streams 0 to 7,

respectively.

FGB[4:11] pins correspond to output drive enables for the MVIP DSi streams 0 to 7,

respectively.

FGx[0:3] are programmable output pins. The least significant four bits of FRMx_MODE register

are driven out pins FGx[0:3] (with bit 0 corresponding to pin FGx[0] etc.).

Normal Framing

Frame groups A&B (FGx[0:11]) are programmed as output framing pulses for use with the local

serial data streams (see Figure 19 - “Frame Pulse Timing for Mode 2” ). The position of the first

framing signal in a group is determined by an 11 bit quantity. The quantity is the FMIC state

number minus one. The quantity determines when the first framing signal in a group is to be

asserted high.

Inverted Framing

Identical to Normal Framing except the polarity of the framing pulses is logically inverted.

Table 13

-

Frame Group Mode bits

1 [01]

2 [10]

3 [11]

Bit

Name

Description

Frame Start (FRMx_STRT) Register x

7:0

PROG_OUT(7:0)

Frame Mode (FRMx_MODE) Register x

7:6

MODE

All 8 bits are driven out FGx[7:0]

Frame Group Mode

0 [00] Programmed Output

5:4

3:0

RESERVED

PROG_OUT(11:8)

All 4 bits are driven out FGx[11:8]

Table 14

-

Frame Register bits for mode 0

Bit

Name

Description

Frame Start (FRMx_STRT) Register x

7:0

RESERVED

Frame Mode (FRMx_MODE) Register x

7:6

MODE

Frame Group Mode

1 [01] DSi/DSo output enable

5:4

3:0

RESERVED

PROG_OUT(3:0)

All 4 bits are driven out FGx[3:0]

Table 15 - Frame Register bits for mode 1

相關PDF資料 |

PDF描述 |

|---|---|

| MT90812 | Integrated Digital Switch (IDX)(集成數(shù)字開關) |

| MT90840AK | Distributed Hyperchannel Switch |

| MT90840AP | Distributed Hyperchannel Switch |

| MT9085B | PAC - Parallel Access Circuit(并行存取電路) |

| MT9092 | Digital Telephone with HDLC(數(shù)字電話(帶高階數(shù)據(jù)鏈路控制HDLC)) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MT90810AK | 制造商:Microsemi Corporation 功能描述: |

| MT90812 | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:Integrated Digital Switch (IDX) |

| MT90812AL | 制造商:Microsemi Corporation 功能描述:SWIT FABRIC 192 X 192 16.384MBPS 5V 64MQFP - Trays 制造商:Zarlink Semiconductor Inc 功能描述:SWIT FABRIC 192 X 192 16.384MBPS 5V 64MQFP - Trays |

| MT90812AL1 | 制造商:Microsemi Corporation 功能描述:SWIT FABRIC 192 X 192 16.384MBPS 5V 64MQFP - Trays 制造商:Microsemi Corporation 功能描述:PB FREE INTEGRATED DIGITAL SWITCH |

| MT90812AP | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:Integrated Digital Switch (IDX) |

發(fā)布緊急采購,3分鐘左右您將得到回復。