- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378056 > PM7383 (PMC-Sierra, Inc.) FRAME ENGINE AND DATA LINK MANAGER 32A256 PDF資料下載

參數(shù)資料

| 型號: | PM7383 |

| 廠商: | PMC-Sierra, Inc. |

| 英文描述: | FRAME ENGINE AND DATA LINK MANAGER 32A256 |

| 中文描述: | 框架引擎和數(shù)據(jù)鏈路管理32A256 |

| 文件頁數(shù): | 195/231頁 |

| 文件大小: | 1947K |

| 代理商: | PM7383 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁當(dāng)前第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁第219頁第220頁第221頁第222頁第223頁第224頁第225頁第226頁第227頁第228頁第229頁第230頁第231頁

RELEASED

DATASHEET

PM7383 FREEDM-32A256

ISSUE 1

PMC-2010336

FRAME ENGINE AND DATA LINK MANAGER 32A256

PROPRIETARY AND CONFIDENTIAL

187

12

FUNCTIONAL TIMING

12.1 Receive H-MVIP Link Timing

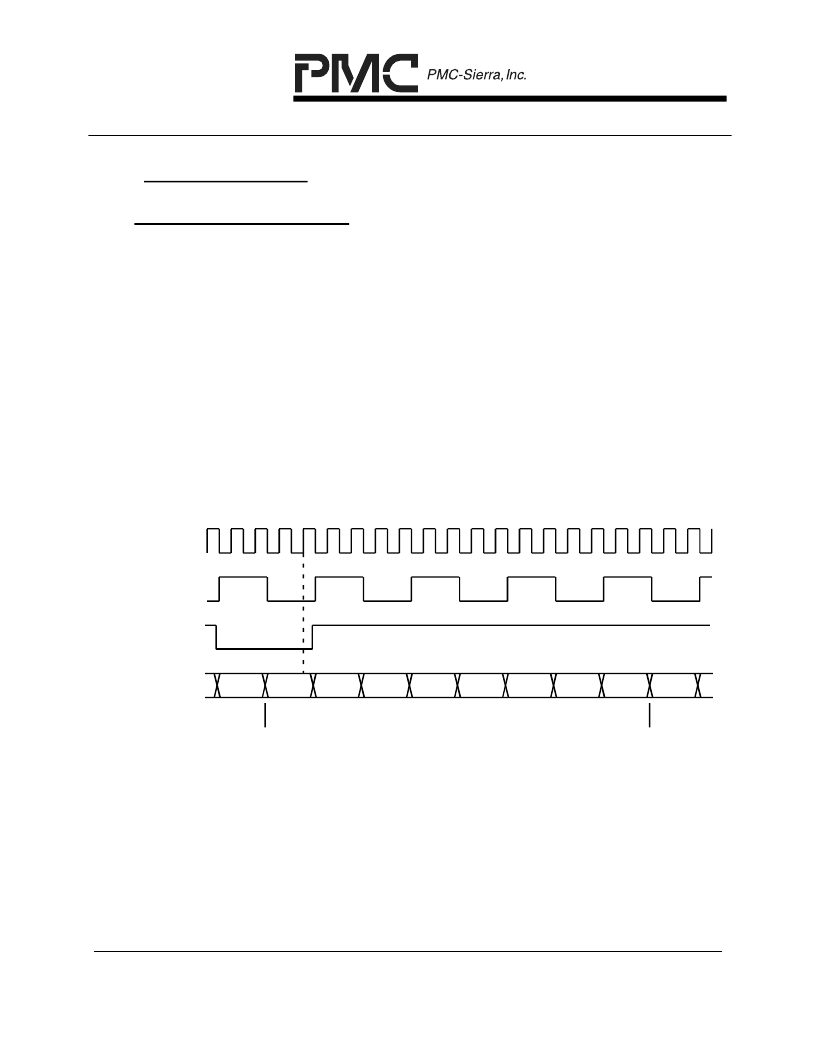

The timing relationship of the receive data clock (RMV8DC), frame pulse clock

(RMV8FPC), data (RD[n]) and frame pulse (RFP8B) signals of a link configured

for 8.192 Mbps H-MVIP operation with a type 0 frame pulse is shown in Figure

12. The falling edges of each RMV8FPC are aligned to a falling edge of the

corresponding RMV8DC for 8.192 Mbps H-MVIP operation. The FREEDM-

32A256 samples RFP8B low on the falling edge of RMV8FPC and references

this point as the start of the next frame. The FREEDM-32A256 samples the data

provided on RD[n] at the point of the data bit using the rising edge of RMV8DC

as indicated for bit 1 (B1) of time-slot 0 (TS 0) in Figure 12. B1 is the most

significant bit and B8 is the least significant bit of each octet. Time-slots can be

ignored by setting the PROV bit in the corresponding word of the receive channel

provision RAM in the RCAS256 block to low.

Figure 12 – Receive 8.192 Mbps H-MVIP Link Timing

RMV8DC

(16 MHz)

RFP8B

RD[n]

B8

B1

B2

B3

B4

B5

B6

B7

B8

B1

TS 127

TS 0

TS 1

RMV8FPC

(4 MHz)

The timing relationship of the receive data clock (RMVCK[n]), data (RD[m], where

8n m 8n+7) and frame pulse (RFPB[n]) signals of a link configured for 2.048

Mbps H-MVIP operation with a type 0 frame pulse is shown in Figure 13. The

FREEDM-32A256 samples RFPB[n] low on the falling edge of the corresponding

RMVCK[n] and references this point as the start of the next frame. The

FREEDM-32A256 samples the data provided on RD[m] at the point of the data

bit using the rising edge of the corresponding RMVCK[n] as indicated for bit 1

(B1) of time-slot 0 (TS 0) in Figure 13. B1 is the most significant bit and B8 is the

least significant bit of each octet. Time-slots can be ignored by setting the PROV

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PM7383-PI | FRAME ENGINE AND DATA LINK MANAGER 32A256 |

| PM7384 | Frame Engine and Data Link Manager |

| PM7384-BI | FRAME ENGINE AND DATA LINK MANAGER 84P672 |

| PM7385 | Frame Engine and Data Link Manager |

| PM7385-BI | 84 LINK, 672 CHANNEL FRAME ENGINE AND DATA LINK MANAGER WITH ANY-PHY PACKET INTERFACE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PM7383-PI | 制造商:PMC 制造商全稱:PMC 功能描述:FRAME ENGINE AND DATA LINK MANAGER 32A256 |

| PM7384 | 制造商:PMC 制造商全稱:PMC 功能描述:Frame Engine and Data Link Manager |

| PM7384-BI | 制造商:PMC 制造商全稱:PMC 功能描述:FRAME ENGINE AND DATA LINK MANAGER 84P672 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。