- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄378193 > RS5C62 (RICOH COMPANY LTD) REAL-TIME CLOCK PDF資料下載

參數(shù)資料

| 型號(hào): | RS5C62 |

| 廠商: | RICOH COMPANY LTD |

| 元件分類(lèi): | XO, clock |

| 英文描述: | REAL-TIME CLOCK |

| 中文描述: | 1 TIMER(S), REAL TIME CLOCK, PDSO20 |

| 封裝: | SSOP-20 |

| 文件頁(yè)數(shù): | 26/48頁(yè) |

| 文件大?。?/td> | 419K |

| 代理商: | RS5C62 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)當(dāng)前第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)

22

RP/RF/RS5C62

5. Interrupts

Interrupts are available in the following two types:

1) Alarm interrupt: Requested upon driving low (turning on) the INTR pin in matching between preset alarm time

(in minutes and hours) and time indicated by the time counter (in minutes and hours).

2) Cyclic interrupt: Requested upon driving low (turning on) the INTR pin with a preset cycle.

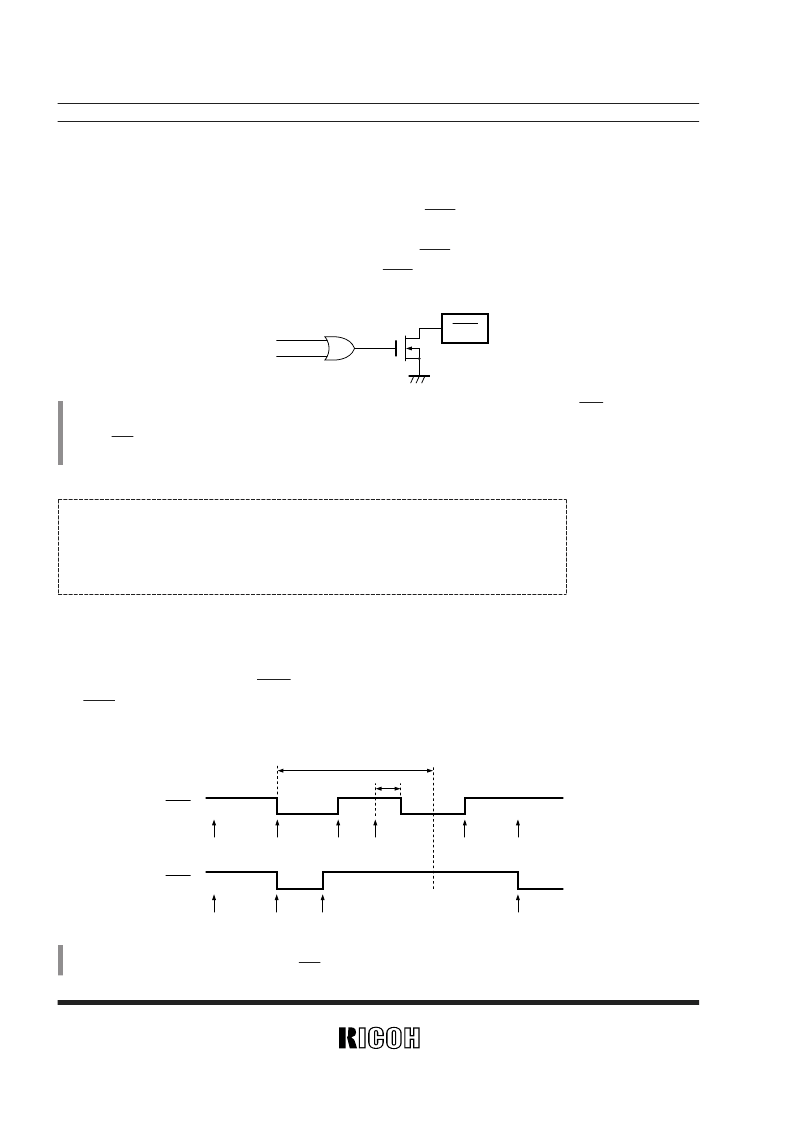

To output an alarm interrupt and a cyclic interrupt, the INTR pin is configured as shown in the figure below:

*

1) When an alarm interrupt and a cyclic interrupt are generated in combination, their logical sum (OR) is output from the INTR pin. In this event, they

can be distinguished from each other by reading the ALFG and CTFG bits of the control register 2.

*

2) The INTR pin output has indefinite states at power-on from 0V.

*

3) An alarm interrupt and a cyclic interrupt are both enabled whether the CE pin input is held high or low.

*

1) The above figure assumes that an alarm interrupt occurs in the absence of a cyclic interrupt.

*

2) The ALFG bit has an inverse logic from that of the INTR pin output.

INTR

Alarm interrupt

Cyclic interrupt

5.1 Alarm Interrupt

Desired alarm time (in minutes and hours) can be preset in the alarm digits of the alarm register with the ALEN

bit set to “0” and then to “1” in the control register 1. Upon matching between the preset alarm time and the time

indicated by the time counter, the INTR pin is driven low (turned on) to output a request for an alarm interrupt.

The INTR pin output can be controlled by using the ALEN bit in the control register 1 and the ALFG bit in the con-

trol register 2.

ALEN=1

ALEN=1

ALEN=0

ALFG=0

ALEN=1

ALEN=0

Alarm time match

Alarm time match

Alarm time match

Alarm time match

INTR

MAX.61.1μs

INTR

Alarm time match period: 1 minute

Alarm-time................Alarm register

(See

“

2. 6 Alarm Register”.)

(See “2. 1 Control Register 1”.)

(See “2. 2 Control Register 2”.)

(See “2. 5 Control Register 2”.)

(See “2. 2 Control Register 2”.)

ALEN bi

ALFG bit

Cyclic.......................Cyclic interrupt select register

CTFG bit

Interrupt Registers

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| RSBL-9-S | Using Permanent Magnet, High sensitivity Two Poles Signal Relay RSB RELAYS |

| RSB-12 | Using Permanent Magnet, High sensitivity Two Poles Signal Relay RSB RELAYS |

| RSB-12-S | Using Permanent Magnet, High sensitivity Two Poles Signal Relay RSB RELAYS |

| RSB-24 | Using Permanent Magnet, High sensitivity Two Poles Signal Relay RSB RELAYS |

| RSB-24-S | Using Permanent Magnet, High sensitivity Two Poles Signal Relay RSB RELAYS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| RS5CLAMP | 制造商:Dialight 功能描述: |

| RS5D | 制造商:LUGUANG 制造商全稱(chēng):Shenzhen Luguang Electronic Technology Co., Ltd 功能描述:Surface Mount Rectifiers |

| RS5D-10 | 制造商:TE Connectivity 功能描述: |

| RS5D-10,000 OHMS | 制造商:TE Connectivity 功能描述: |

| RS5D-10000 OHMS | 制造商:TE Connectivity 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。