- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379352 > SC16C852SVIET (NXP SEMICONDUCTORS) 1.8 V dual UART, 20 Mbit-s (max.) with 128-byte FIFOs, infrared (IrDA), and XScale VLIO bus interface PDF資料下載

參數(shù)資料

| 型號(hào): | SC16C852SVIET |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 1.8 V dual UART, 20 Mbit-s (max.) with 128-byte FIFOs, infrared (IrDA), and XScale VLIO bus interface |

| 中文描述: | 2 CHANNEL(S), 5M bps, SERIAL COMM CONTROLLER, PBGA36 |

| 封裝: | 3.50 X 3.50 MM, 0.80 MM HEIGHT, ROHS COMPLIANT, PLASTIC, SOT-912-1, TFBGA-36 |

| 文件頁(yè)數(shù): | 9/48頁(yè) |

| 文件大?。?/td> | 221K |

| 代理商: | SC16C852SVIET |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)當(dāng)前第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)

SC16C852SV_1

NXP B.V. 2008. All rights reserved.

Product data sheet

Rev. 01 — 23 September 2008

9 of 48

NXP Semiconductors

SC16C852SV

Dual UART with 128-byte FIFOs, IrDA, and XScale VLIO bus interface

[1]

These registers are accessible only when LCR[7] is a logic 0.

[2]

These registers are accessible only when LCR[7] is a logic 1.

[3]

Second special register are accessible only when EFCR[0] = 1.

[4]

Enhanced feature registers are only accessible when LCR = 0xBF.

[5]

First extra feature registers are only accessible when EFCR[2:1] = 01b.

[6]

Second extra feature registers are only accessible when EFCR[2:1] = 10b.

6.4 FIFO operation

6.4.1

32-byte FIFO mode

When all four of these registers (TXINTLVL, RXINTLVL, FLWCNTH, FLWCNTL) in the

First Extra Register Set are empty (0x00) the transmit and receive trigger levels are set by

FCR[7:4]. In this mode the transmit and receive trigger levels are backward compatible to

the SC16C652B (see

Table 5

), and the FIFO sizes are 32 entries. The transmit and

receive data FIFOs are enabled by the FIFO Control Register bit 0 (FCR[0]). It should be

noted that the user can set the transmit trigger levels by writing to the FCR, but activation

will not take place until EFR[4] is set to a logic 1. The receiver FIFO section includes a

time-out function to ensure data is delivered to the external CPU (see

Section 6.8

). Please

refer to

Table 10

and

Table 11

for the setting of FCR[7:4].

6.4.2

128-byte FIFO mode

When either TXINTLVL, RXINTLVL, FLWCNTH or FLWCNTL in the First Extra Register

Set contains any value other than 0x00, the transmit and receive trigger levels are set by

TXINTLVL and RXINTLVL registers. TXINTLVL sets the trigger levels for the transmit

FIFO, and the transmit trigger levels can be set to any value between 1 and 128 with

granularity of 1. RXINTLVL sets the trigger levels for the receive FIFO, the receive trigger

levels can be set to any value between 1 and 128 with granularity of 1.

When the effective FIFO size changes (that is, when FCR[0] toggles or when the

combined content of TXINTLVL, RXINTLVL, FLWCNTH and FLWCNTL changes between

equal and unequal to 0x00), both RX FIFO and TX FIFO will be reset (data in the FIFO will

be lost).

6.5 Hardware flow control

When automatic hardware flow control is enabled, the SC16C852SV monitors the CTSx

pin for a remote buffer overflow indication and controls the RTSx pin for local buffer

overflows. Automatic hardware flow control is selected by setting EFR[6] (RTS) and

EFR[7] (CTS) to a logic 1. If CTSx transitions from a logic 0 to a logic 1 indicating a flow

control request, ISR[5] will be set to a logic 1 (if enabled via IER[7:6]), and the

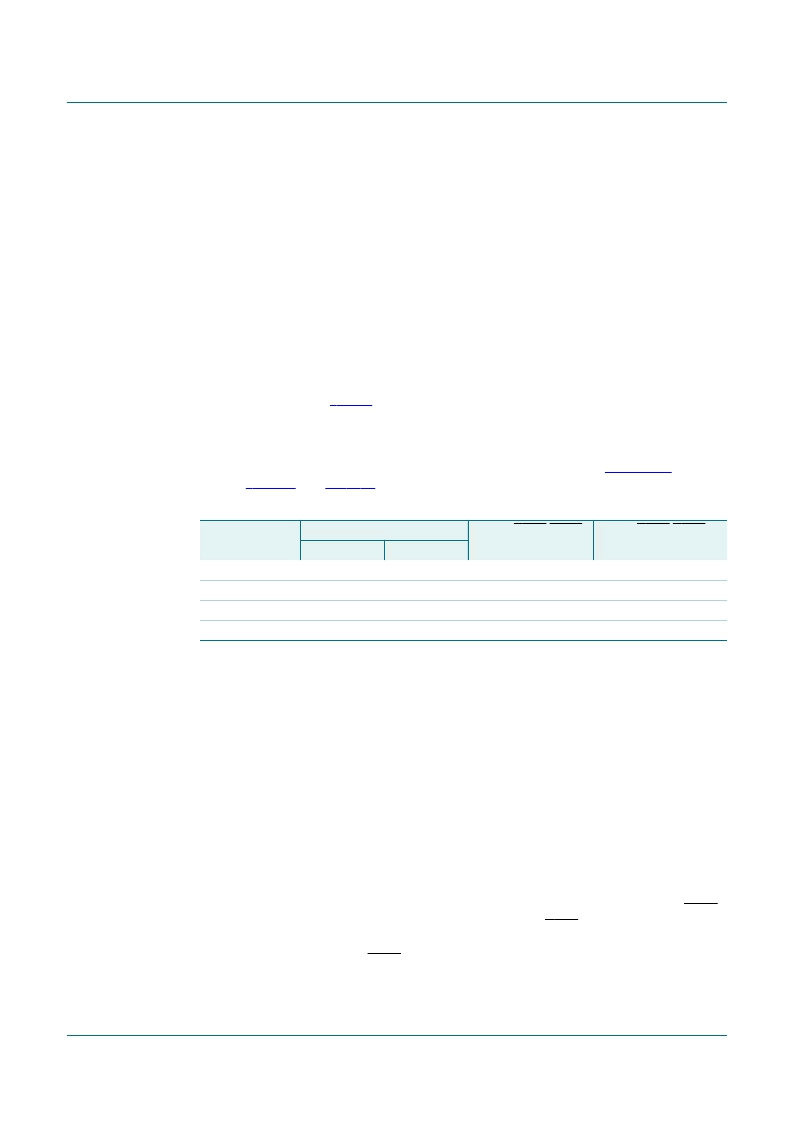

Table 5.

(FCR[7:6, 5:4])

Interrupt trigger level and Flow control mechanism

INTA/INTB pin activation

RX

TX

8

16

16

8

24

24

28

30

Negate RTSA/RTSB

or send Xoff

Assert RTSA/RTSB

or send Xon

[00, 00]

[01, 01]

[10, 10]

[11, 11]

8

16

24

28

0

7

15

23

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SC16C852VIET | 1.8 V dual UART, 5 Mbit-s (max.) with 128-byte FIFOs, infrared (IrDA) and XScale VLIO bus interface |

| SC16IS740IPW | Single UART with I2C-bus-SPI interface, 64 bytes of transmit and receive FIFOs, IrDA SIR built-in support |

| SC16IS750IBS | Single UART with I2C-bus-SPI interface, 64 bytes of transmit and receive FIFOs, IrDA SIR built-in support |

| SC16IS750IPW | Single UART with I2C-bus-SPI interface, 64 bytes of transmit and receive FIFOs, IrDA SIR built-in support |

| SC16IS760IBS | Single UART with I2C-bus-SPI interface, 64 bytes of transmit and receive FIFOs, IrDA SIR built-in support |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SC16C852SVIET,115 | 功能描述:UART 接口集成電路 UART 2-CH 128Byte FIFO 1.8V 36-Pin RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| SC16C852SVIET,151 | 功能描述:UART 接口集成電路 UART 2-CH 128Byte FIFO 1.8V 36-Pin RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| SC16C852SVIET,157 | 功能描述:UART 接口集成電路 UART 2-CH 128Byte FIFO 1.8V 36-Pin RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| SC16C852V | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Dual UART with 128-byte FIFOs, IrDA, and XScale VLIO bus interface |

| SC16C852V_08 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:1.8 V dual UART, 5 Mbit/s (max.) with 128-byte FIFOs, infrared (IrDA), and XScale VLIO bus interface |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。