- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98144 > ST6375B1/XXX (STMICROELECTRONICS) 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP42 PDF資料下載

參數(shù)資料

| 型號(hào): | ST6375B1/XXX |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP42 |

| 封裝: | SHRINK, PLASTIC, DIP-42 |

| 文件頁(yè)數(shù): | 27/84頁(yè) |

| 文件大小: | 861K |

| 代理商: | ST6375B1/XXX |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)當(dāng)前第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)

33/84

ST6365, ST6375, ST6385 ST6367, ST6377, ST6387

TIMERS (Cont’d)

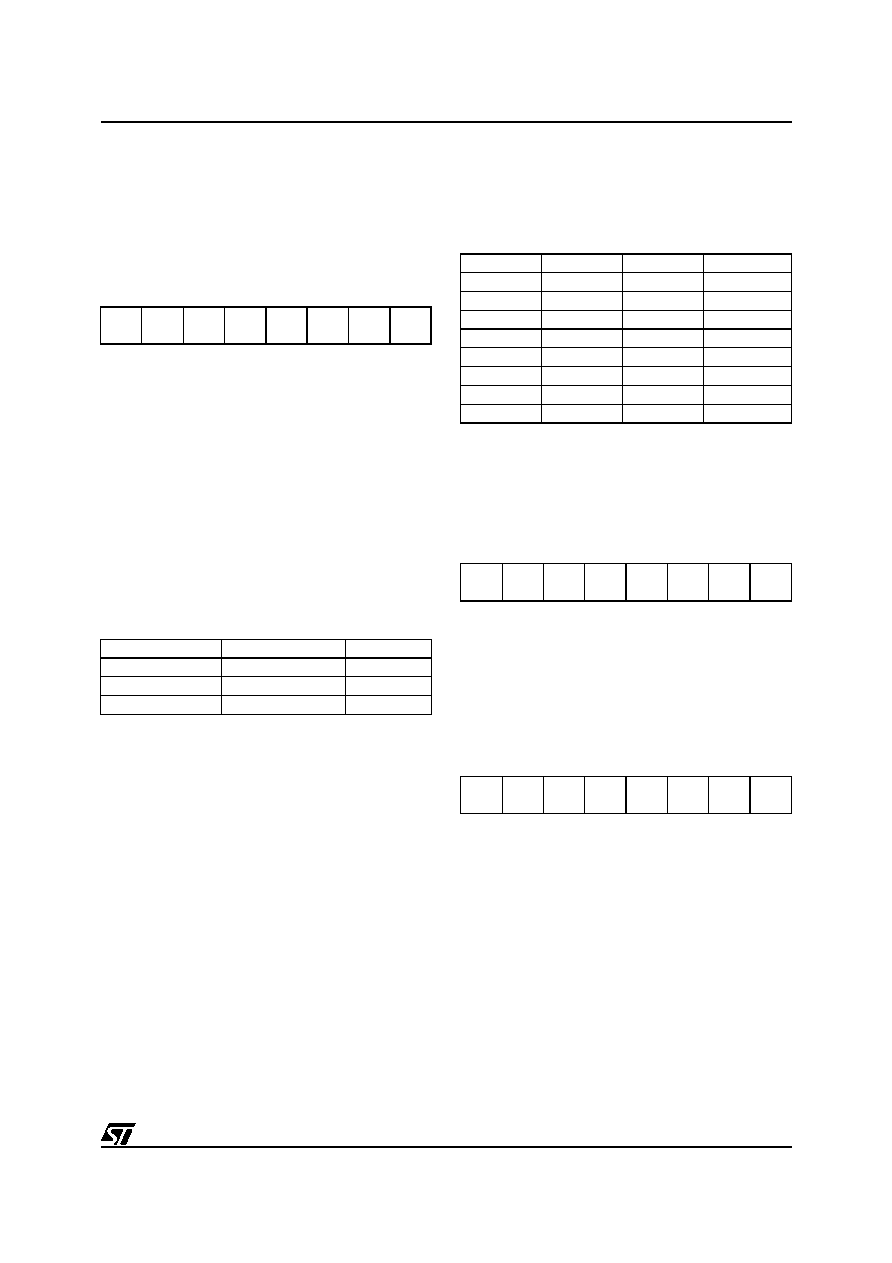

4.2.2 Timer Status Control Registers (TSCR)

Timers 1 and 2

Address: D4h (Timer 1), DCh (Timer 2) - Read/

Write

Reset Value: 00h

TMZ. Low-to-high transition indicates that the tim-

er count register has decremented to zero. This bit

must be cleared by user software before to start

with a new count.

ETI. This bit, when set, enables the timer interrupt

(vector #3 for Timer 1, vector #2 for Timer 2 re-

quest). If ETI=0 the timer interrupt is disabled. If

ETI= 1 and TMZ= 1 an interrupt request is gener-

ated.

D5. This is the timers enable bit D5. It must be

cleared to 0 together with a set to 1 of bit D4 to en-

able Timer 1 and Timer 2 functions. It is not imple-

mented on registers TSCR2.

D4. This is the timers enable bit D4. This bit must

be set to 1 together with a clear to 0 of bit D5 to en-

able all Timers (Timer 1 and 2) functions. It is not

implemented on registers TSCR2.

PSI. Used to initialize the prescaler and inhibit its

counting while PSI = 0 the prescaler is set to 7Fh

and the counter is inhibited. When PSI = 1 the

prescaler is enabled to count downwards. As long

as PSI= 0 both counter and prescaler are not run-

ning.

PS2-PS0. These bits select the division ratio of the

prescaler register. (see Table 11)

The TSCR1 and TSCR2 registers are cleared on

reset. The correct D4-D5 combination must be

written in TSCR1 by user's software to enable the

operation of Timer 1 and 2.

Table 11. Prescaler Division Factors

4.2.3 Timer Counter Registers (TCR)

Timer Counter 1 and 2

Address: D3h (Timer Counter 1), DBh (Timer

Counter 2) - Read/Write

Reset Value: FFh

Bit 7-0 = D7-D0: Counter Bits.

4.2.4 Timer Prescaler Registers (PSCR)

Timer Prescalers 1 and 2

Address: D2h (Timer Prescaler 1), DAh (Timer

Prescaler 2) - Read/Write

Reset Value: 7Fh

Bit 7 = D7: Always read as "0".

Bit 6-0 = D6-D0: Prescaler Bits.

70

TMZ

ETI

D5

D4

PSI

PS2

PS1

PS0

D5

D4

Timers

0

Disabled

0

1

Enabled

1

X

Reserved

PS2

PS1

PS0

Divided By

000

1

001

2

010

4

011

8

10016

10132

11064

111

128

70

D7

D6

D5

D4

D3

D2

D1

D0

70

D7

D6

D5

D4

D3

D2

D1

D0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ST6367B1/XXX | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP42 |

| ST6382B1/XXX | 8-BIT, MROM, MICROCONTROLLER, PDIP42 |

| ST6386B1 | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP42 |

| ST6388B1 | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP42 |

| ST6387B1 | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PDIP42 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ST6377 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:8-BIT MCUs WITH ON-SCREEN-DISPLAY FOR TV TUNING |

| ST6377B1/XXX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| ST63-7-W1-22-9-120 | 制造商:TE Connectivity 功能描述:ST63-7-W1-22-9-120 |

| ST63-7-W1-22-9-120CS28 | 制造商:TE Connectivity 功能描述:E53797N001 |

| ST63-7-W1-22-9-120CS2894 | 制造商:TE Connectivity 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。