- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98229 > THS8083-95CPZP (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQFP100 PDF資料下載

參數(shù)資料

| 型號: | THS8083-95CPZP |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 消費家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| 封裝: | POWER, THERMALLY ENHANCED, PLASTIC, TQFP-100 |

| 文件頁數(shù): | 14/61頁 |

| 文件大?。?/td> | 239K |

| 代理商: | THS8083-95CPZP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁

2–7

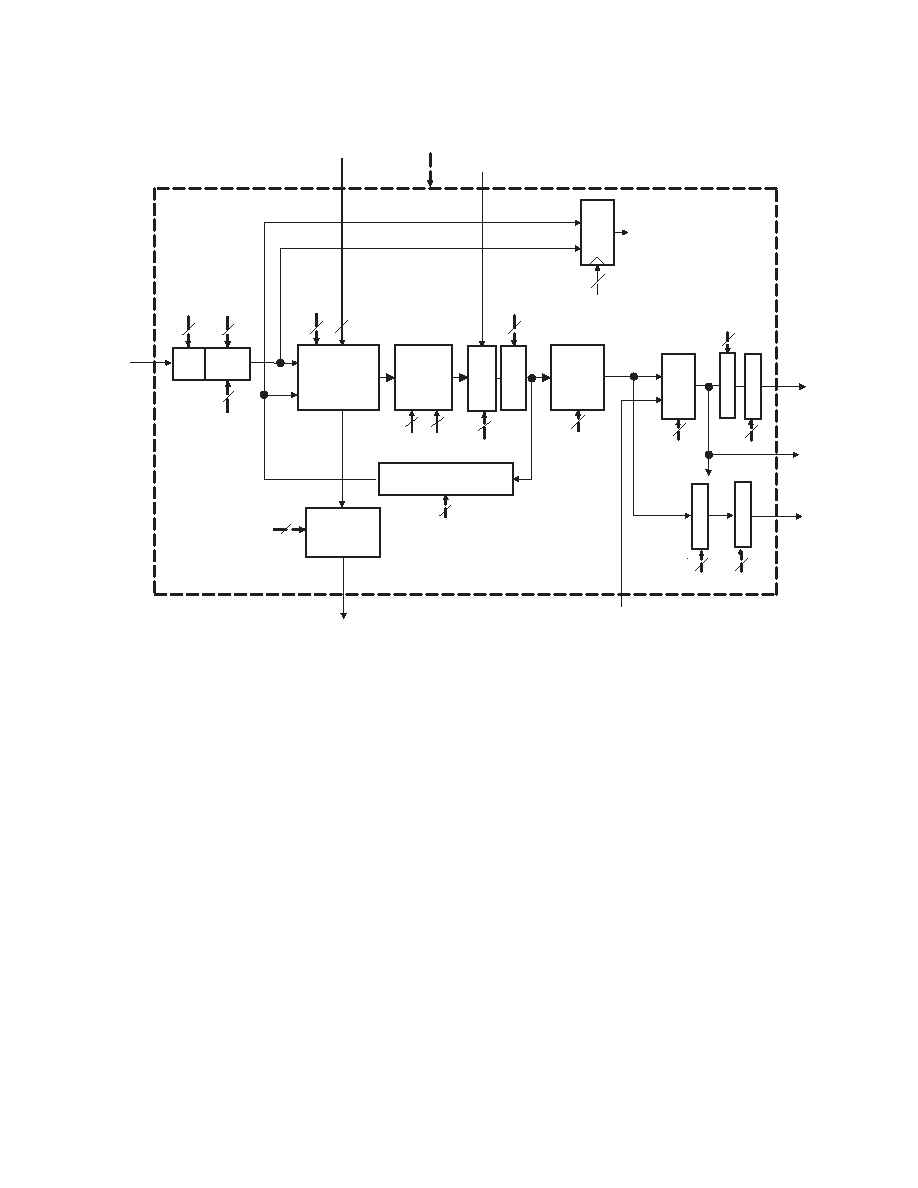

Phase-

Frequency

Detector

HS

Programmable

Divider

MUX

I

N

V

POL

PROG.

LOOP

FILTER

PFD_FREEZE

LOCK

12

to ADC

MUX

ADCCLK1

(see NOTE)

ADCCLK2

DTOCLK3

DTO

EXT_ADCCLK

Phase

Selector

INV2

1

HS_POL

TERM_CNT

PHASESEL

SEL_ADCCLK

DIV3

1

INV3

1

D

I

V

2

DIV2

1

PLLCLK

GAIN_N

3

33

GAIN_P

NOM_INC

SELCLK

DTO_DIS

I

N

V

D

I

V

2

1

Noise

Gate

1

HS_MS

HS_WIDTH

3 P

5

1

DIGITAL PLL

1

DISABLE_

DIV

3

Lock

Detection

Hysteresis

LD_THRESH

8

VCOCLK

(From Analog PLL)

NOTE: ADCCLK1 is used by the output formatter to generate the DATACLK1 output.

1

DHS_MODE

8

Compensated in Output

Formatter for Pipeline

Data Delay. Then output

on Terminal DHS With

Polarity Determined by

<DHS_POL>.

PFD

Figure 2–6. Digital PLL

The device provides three clock outputs. One of these output signals, DATACLK1, is derived from the ADC clock

output. It is actually equal to the sampling clock but compensated in phase so that its rising edge always corresponds

to the center valid region of the output data. Output data timing (setup/hold) is specified with respect to this rising edge.

Therefore, DATACLK1 is typically used for clocking the THS8083’s output data. The frequency of DATACLK1 will be

either equal or 1/2 of the sampling clock, depending on the operation mode of the output formatter. When the

THS8083 is clocked with an external sampling clock, this external clock is used as the source to generate DATACLK1

in the output formatter.

The second clock output, ADCCLK2, is equal to the ADC sampling clock but can optionally be divided by 2 and

inverted.

Finally, the third clock output, DTOCLK3, is always derived from the PLL output clock, irrespective of the use of an

external sampling clock on EXT_ADCCLK. So, when operating with an external sampling clock, the DTOCLK3 output

can be used to generate a second, possibly asynchronous, clock signal in either open loop operation or in closed loop

locked to a reference HS input. Also, DTOCLK3 can be optionally divided by 2 and inverted.

相關PDF資料 |

PDF描述 |

|---|---|

| THS8083APZP | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| THS8083APZPG4 | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| THS8083CPZP | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| THS8133ACPHP | PARALLEL, WORD INPUT LOADING, 0.005 us SETTLING TIME, 10-BIT DAC, PQFP48 |

| THS8133BCPHP | PARALLEL, WORD INPUT LOADING, 0.005 us SETTLING TIME, 10-BIT DAC, PQFP48 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| THS8083A | 制造商:TI 制造商全稱:Texas Instruments 功能描述:TRIPLE 8 BIT 80 MSPS 3.3V VIDEO AND GRAPHICS |

| THS8083A95 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:TRIPLE 8-BIT, 95MSPS, 3.3V VIDEO AND GRAPHICS |

| THS8083A95PZP | 功能描述:視頻模擬/數(shù)字化轉換器集成電路 Tr 8B 95MSPS 3.3V Vid & Graphics Dig RoHS:否 制造商:Texas Instruments 輸入信號類型:Differential 轉換器數(shù)量:1 ADC 輸入端數(shù)量:4 轉換速率:3 Gbps 分辨率:8 bit 結構: 輸入電壓:3.3 V 接口類型:SPI 信噪比: 電壓參考: 電源電壓-最大:3.45 V 電源電壓-最小:3.15 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:TCSP-48 封裝:Reel |

| THS8083APZP | 功能描述:視頻模擬/數(shù)字化轉換器集成電路 Triple 8B 80 MSPS 3.3V YUV/RGB RoHS:否 制造商:Texas Instruments 輸入信號類型:Differential 轉換器數(shù)量:1 ADC 輸入端數(shù)量:4 轉換速率:3 Gbps 分辨率:8 bit 結構: 輸入電壓:3.3 V 接口類型:SPI 信噪比: 電壓參考: 電源電壓-最大:3.45 V 電源電壓-最小:3.15 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:TCSP-48 封裝:Reel |

| THS8083APZP | 制造商:Texas Instruments 功能描述:8BIT ADC 80MSPS TRIPLE SMD 8083 |

發(fā)布緊急采購,3分鐘左右您將得到回復。