- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98293 > TS83102G0BCGL (E2V TECHNOLOGIES PLC) 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CBGA152 PDF資料下載

參數(shù)資料

| 型號(hào): | TS83102G0BCGL |

| 廠商: | E2V TECHNOLOGIES PLC |

| 元件分類: | ADC |

| 英文描述: | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CBGA152 |

| 封裝: | 21 X 21 MM, 1.27 MM PITCH, CERAMIC, BGA-152 |

| 文件頁(yè)數(shù): | 19/60頁(yè) |

| 文件大?。?/td> | 1510K |

| 代理商: | TS83102G0BCGL |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)當(dāng)前第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)

26

0830E–BDC–06/07

TS83102G0B

e2v semiconductors SAS 2007

An increase in SFDR up to >10 dB with an addition of -23 dBrms DC to 5 MHz out-of-band dither is

noted.

The dither profile has to be defined according to the ADC’s INL pattern as well as the trade-off to be

reached between the increase in SFDR and the loss in SNR.

Please refer to the Application Note on dither for more information on adding dither to an ADC.

10.1.8

Typical Dual Tone Dynamic Performance

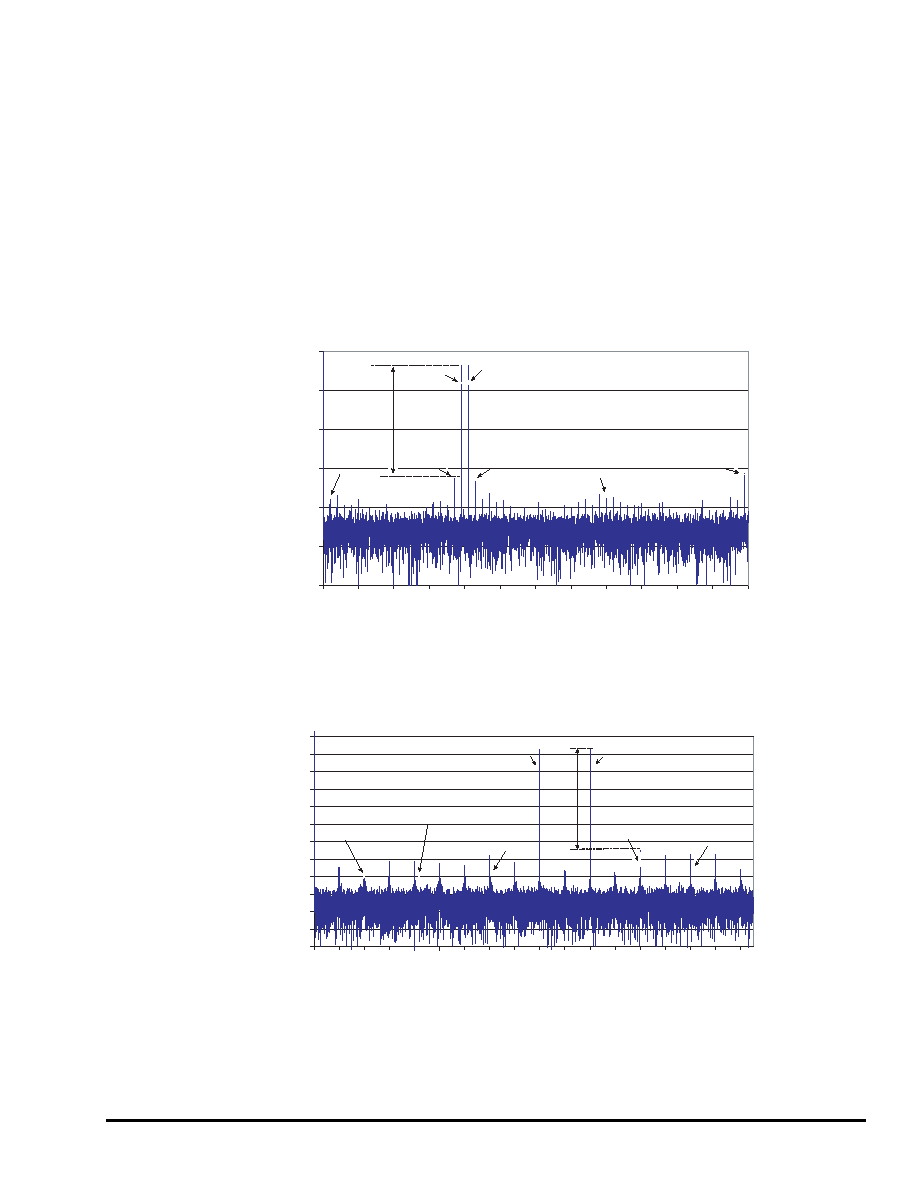

Figure 10-19. Dual Tone Reconstructed Signal Spectrum at Fs = 1.2 Gsps, Fin1 = 995 MHz,

Fin2 = 1005 MHz (-7 dBFS), IMD3 = 64 dBFS

Note:

The output data is not decimated. The spectrum is displayed from DC to 600 MHz.

Figure 10-20. Dual Tone Reconstructed Signal Spectrum at Fs = 1.4 Gsps, Fin1 = 745 MHz,

Fin2 = 755 MHz (-7 dBFS), IMD3 = 65 dBFS

-120

-100

-80

-60

-40

-20

0

50

100

150

200

250

300

350

400

450

500

550

600

Fs (MHz)

dBFS

F2 = Fs - Fin2

= 195 MHz

-7 dBFS

F1 = Fs - Fin1

=205 MHz

-7 dBFS

F1 - F2

10 MHz

-75 dBFS

2F2 - F1

185 MHz

-64 dBFS

2F1 - F2

215 MHz

-65 dBFS

F1 + F2

400 MHz

-73 dBFS

2F2 + F1

595 MHz

-63 dBFS

Fs/2

IMD3

-120

-110

-100

-90

-80

-70

-60

-50

-40

-30

-20

-10

0

5

10

15

20

25

30

35

40

45

50

55

60

65

70

75

80

85

dBFS

2F1 - F2 = 35 MHz

-68 dBFS

2F2 - F1 = 65 MHz

-65 dBFS

F1 - F2 = 10 MHz

-78 dBFS

F1 + F2 = 75 MHz

-68 dBFS

2F2 + F1 = 20 MHz

-72 dBFS

F2 = - 4 x (Fs/8) + Fin2 = 55 MHz

-7 dBFS

F1 = -4 x (Fs/8) + Fin1 = 45 MHz

-7 dBFS

MHz

87.5

= Fs/16

IMD3

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TS83110CZT | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CDFP28 |

| TS83110MZT | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CDFP28 |

| TS83110VZT | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CDFP28 |

| TS83110MZB/T | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CDSO28 |

| TS83110VS | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TS83102G0BVGL | 制造商:e2v technologies 功能描述:ADC SGL 2GSPS 10-BIT PARALLEL 152CBGA - Trays |

| TS83102G0CGL | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog to Digital Converter |

| TS83102G0GSZR5 | 制造商:e2v technologies 功能描述:TS83102G0GSZR5 - Trays |

| TS831-3I | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:MICROPOWER VOLTAGE SUPERVISOR RESET ACTIVE LOW |

| TS831-3ID | 功能描述:監(jiān)控電路 2.71V Micropower AL RoHS:否 制造商:STMicroelectronics 監(jiān)測(cè)電壓數(shù): 監(jiān)測(cè)電壓: 欠電壓閾值: 過(guò)電壓閾值: 輸出類型:Active Low, Open Drain 人工復(fù)位:Resettable 監(jiān)視器:No Watchdog 電池備用開關(guān):No Backup 上電復(fù)位延遲(典型值):10 s 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:UDFN-6 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。