- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98293 > TS83102G0BCGL (E2V TECHNOLOGIES PLC) 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CBGA152 PDF資料下載

參數(shù)資料

| 型號(hào): | TS83102G0BCGL |

| 廠商: | E2V TECHNOLOGIES PLC |

| 元件分類: | ADC |

| 英文描述: | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CBGA152 |

| 封裝: | 21 X 21 MM, 1.27 MM PITCH, CERAMIC, BGA-152 |

| 文件頁數(shù): | 23/60頁 |

| 文件大小: | 1510K |

| 代理商: | TS83102G0BCGL |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當(dāng)前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

3

0830E–BDC–06/07

e2v semiconductors SAS 2007

TS83102G0B

6.

Functional Description

The TS83102G0B is a 10-bit 2 Gsps ADC. The device includes a front-end master/slave Track and Hold

stage (Sample and Hold), followed by an analog encoding stage (Analog Quantizer), which outputs ana-

log residues resulting from analog quantization. Successive banks of latches regenerate the analog

residues into logical levels before entering an error correction circuit and resynchronization stage, fol-

lowed by 50

differential output buffers.

The TS83102G0B works in a fully differential mode from analog inputs to digital outputs. A differential

Data Ready output (DR/DRB) is available to indicate when the outputs are valid and an Asynchronous

Data Ready Reset ensures that the first digitized data corresponds to the first acquisition.

The control pin B/GB (A11 of the CBGA package) is provided to select either a binary or gray data output

format. The gain control pin GA (R9 of the CBGA package) is provided to adjust the ADC gain transfer

function.

A Sampling Delay Adjust function (SDA) may be used to ease the interleaving of ADCs.

A pattern generator is integrated on the chip for debug or acquisition setup. This function is activated

through the PGEB pin (A9 of the CBGA package).

An Out-of-range bit (OR/ORB) indicates when the input overrides 0.5 Vpp.

A selectable decimation by 32 functions is also available for enhanced testability coverage (A10 of the

CBGA package), along with the die junction temperature monitoring function.

The TS83102G0B uses only vertical isolated NPN transistors together with oxide isolated polysilicon

resistors, which allows enhanced radiation tolerance (over 100 kRad (Si) total dose expected tolerance).

7.

Specification

7.1

Absolute Maximum Ratings

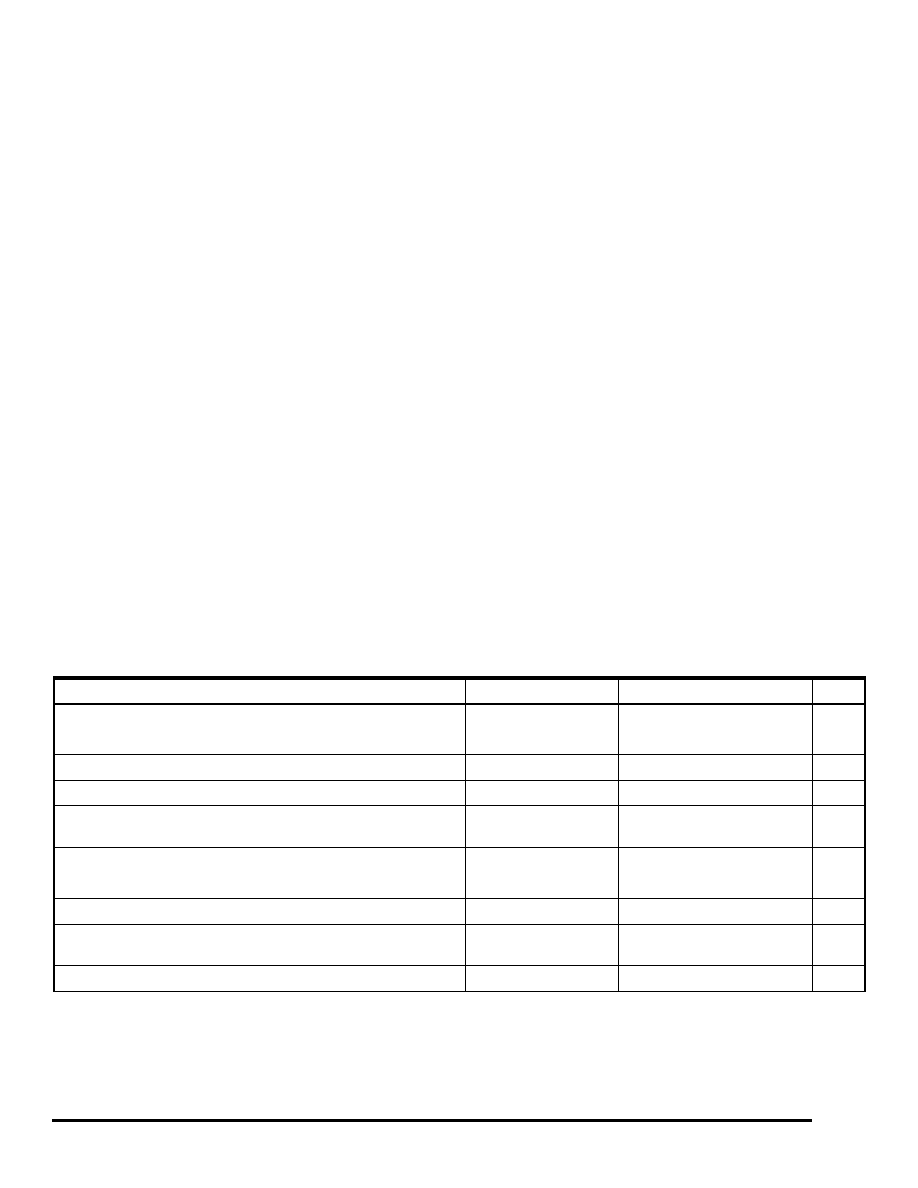

Parameter

Symbol

Comments

Value

Unit

Positive supply voltage

VCC

GND to 6.0

V

Digital negative supply voltage

D

VEE

GND to -5.7

V

Digital positive supply voltage

V

PLUSD

GND - 1.1 to 2.5

V

Negative supply voltage

VEE

GND to -5.5

V

Maximum difference between negative

supply voltages

DVEE to VEE

0.3

V

Analog input voltages

VIN or VINB

-1.5 to 1.5

V

Maximum difference between VIN and VINB

V

IN - VINB

-1.5 to 1.5

V

Clock input voltage

V

CLK or VCLKB

-1 to 1

V

Maximum difference between VCLK and

VCLKB

V

CLK - VCLKB

-1 to 1

Vpp

Static input voltage

VD

GA, SDA

-5 to 0.8

V

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TS83110CZT | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CDFP28 |

| TS83110MZT | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CDFP28 |

| TS83110VZT | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CDFP28 |

| TS83110MZB/T | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CDSO28 |

| TS83110VS | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TS83102G0BVGL | 制造商:e2v technologies 功能描述:ADC SGL 2GSPS 10-BIT PARALLEL 152CBGA - Trays |

| TS83102G0CGL | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog to Digital Converter |

| TS83102G0GSZR5 | 制造商:e2v technologies 功能描述:TS83102G0GSZR5 - Trays |

| TS831-3I | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:MICROPOWER VOLTAGE SUPERVISOR RESET ACTIVE LOW |

| TS831-3ID | 功能描述:監(jiān)控電路 2.71V Micropower AL RoHS:否 制造商:STMicroelectronics 監(jiān)測(cè)電壓數(shù): 監(jiān)測(cè)電壓: 欠電壓閾值: 過電壓閾值: 輸出類型:Active Low, Open Drain 人工復(fù)位:Resettable 監(jiān)視器:No Watchdog 電池備用開關(guān):No Backup 上電復(fù)位延遲(典型值):10 s 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:UDFN-6 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。