- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98293 > TS83102G0BCGL (E2V TECHNOLOGIES PLC) 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CBGA152 PDF資料下載

參數(shù)資料

| 型號: | TS83102G0BCGL |

| 廠商: | E2V TECHNOLOGIES PLC |

| 元件分類: | ADC |

| 英文描述: | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CBGA152 |

| 封裝: | 21 X 21 MM, 1.27 MM PITCH, CERAMIC, BGA-152 |

| 文件頁數(shù): | 45/60頁 |

| 文件大小: | 1510K |

| 代理商: | TS83102G0BCGL |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁當(dāng)前第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

5

0830E–BDC–06/07

e2v semiconductors SAS 2007

TS83102G0B

7.3

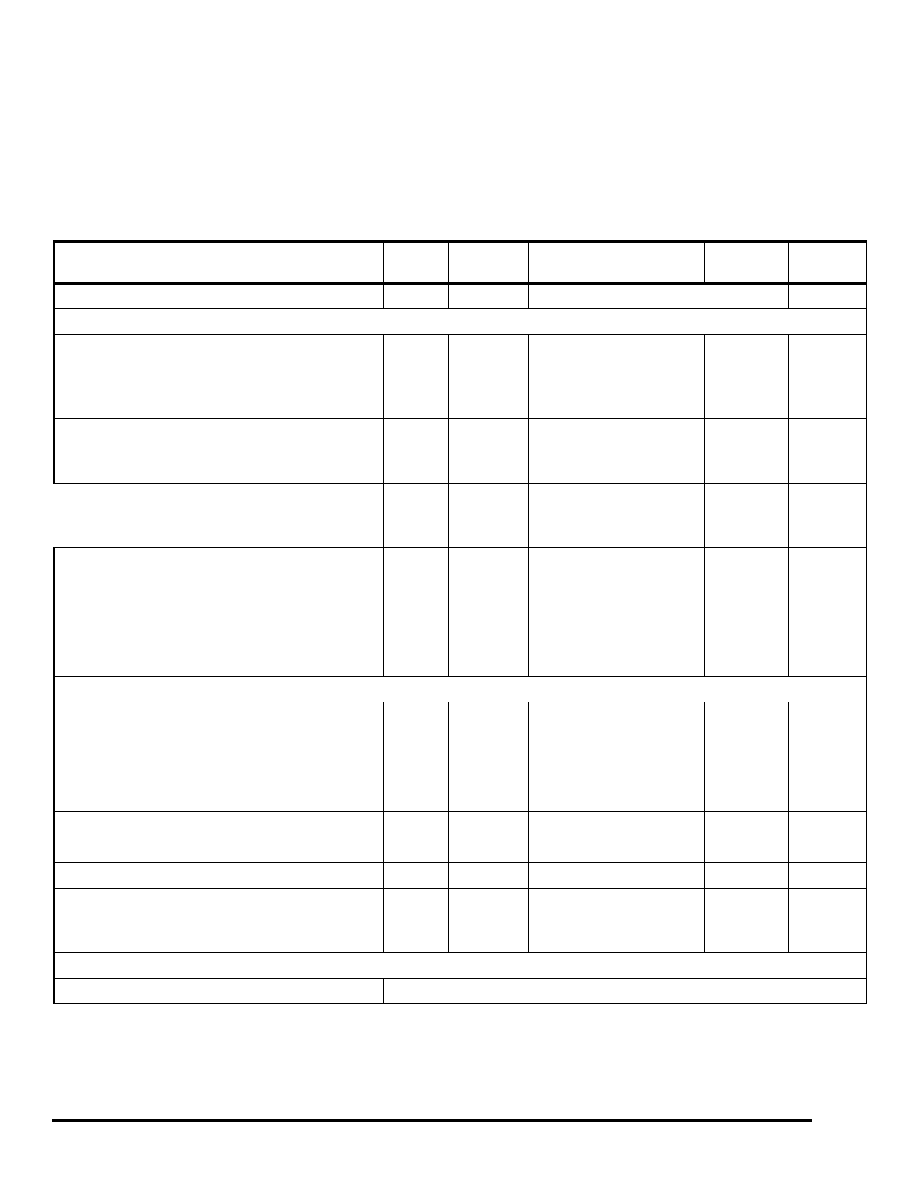

Electrical Operating Characteristics

V

CC = 5V ; VPLUSD = 0V (unless otherwise specified). ADC performances are independent of VPLUSD common mode

voltage and performances are guaranteed within the limits of the specified V

PLUSD range (from -0.9V to 1.7V);

V

EE = DVEE = -5V; VIN - VINB = 500 mVpp (full-scale single-ended or differential input);

clock inputs differential driven; analog-input single-ended driven.

Parameter

Test

Level

Symbol

Min

Typ

Max

Unit

Resolution

10

Bits

Power Requirements

Positive supply voltage

- analog

- digital (ECL)

- digital (LVDS)

1

4

V

CC

VPLUSD

4.75

5

- 0.8

1.45

5.25

V

Positive supply current

- analog

- digital

1

IVCC

I

VPLUSD

138

154

205

200

mA

Negative supply voltage

- analog

- digital

1

V

EE

DVEE

-5.25

-5

-4.75

V

Negative supply current

- analog

- digital

1

VEE

IDVEE

615

160

750

200

mA

Power dissipation

- ECL

- LVDS

1

4

P

D

4.6

5.0

5.2

5.7

W

Analog Inputs

Full-scale input voltage range (differential mode)

(0 V common mode voltage)

4

V

IN,

VINB

- 125

125

mV

Full-scale input voltage range (single-ended input

option)

(0 V common mode voltage)

4

V

IN,

V

INB

- 250

0

250

mV

Analog input power level (50

single-ended)

4

PIN

- 2

dBm

Analog input capacitance (die)

4

C

IN

0.3

pF

Input leakage current

4

I

IN

10

A

Input resistance

- single-ended

- differential

4

R

IN

R

IN

49

98

50

100

51

102

Clock Inputs

Logic common mode compatibility for clock inputs

Differential ECL to LVDS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TS83110CZT | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CDFP28 |

| TS83110MZT | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CDFP28 |

| TS83110VZT | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CDFP28 |

| TS83110MZB/T | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CDSO28 |

| TS83110VS | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TS83102G0BVGL | 制造商:e2v technologies 功能描述:ADC SGL 2GSPS 10-BIT PARALLEL 152CBGA - Trays |

| TS83102G0CGL | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog to Digital Converter |

| TS83102G0GSZR5 | 制造商:e2v technologies 功能描述:TS83102G0GSZR5 - Trays |

| TS831-3I | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:MICROPOWER VOLTAGE SUPERVISOR RESET ACTIVE LOW |

| TS831-3ID | 功能描述:監(jiān)控電路 2.71V Micropower AL RoHS:否 制造商:STMicroelectronics 監(jiān)測電壓數(shù): 監(jiān)測電壓: 欠電壓閾值: 過電壓閾值: 輸出類型:Active Low, Open Drain 人工復(fù)位:Resettable 監(jiān)視器:No Watchdog 電池備用開關(guān):No Backup 上電復(fù)位延遲(典型值):10 s 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:UDFN-6 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。