- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359354 > VDP31XXB (MICRONAS SEMICONDUCTOR HOLDING AG) Video Processor Family PDF資料下載

參數(shù)資料

| 型號(hào): | VDP31XXB |

| 廠商: | MICRONAS SEMICONDUCTOR HOLDING AG |

| 英文描述: | Video Processor Family |

| 中文描述: | 視頻處理器系列 |

| 文件頁數(shù): | 31/72頁 |

| 文件大小: | 597K |

| 代理商: | VDP31XXB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當(dāng)前第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁

PRELIMINARY DATA SHEET

VDP 31xxB

31

Micronas

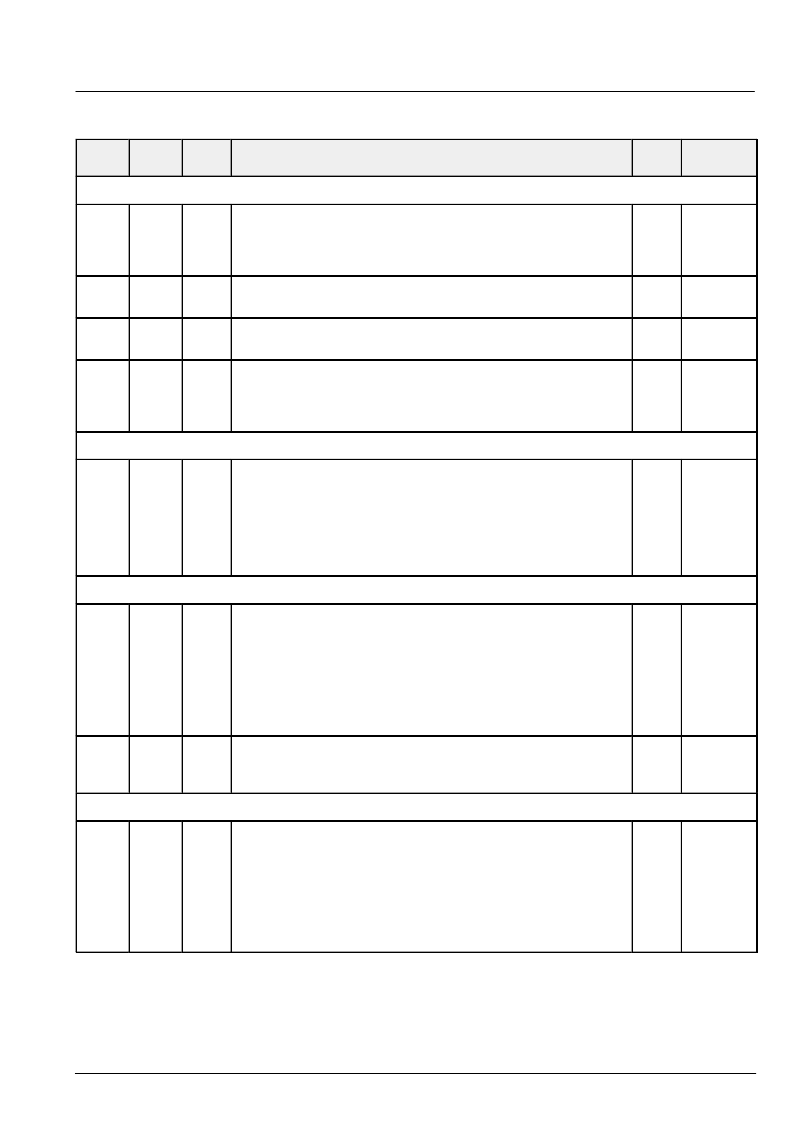

Table 3

–

1:

I

2

C control and status registers of front-end

I

2

C Sub

address

Number

of bits

Mode

Function

Default

Name

FP INTERFACE

h

’

35

8

r

FP status

bit [0]

bit [1]

bit [2]

write request

read request

busy

FPSTA

h

’

36

16

w

bit[8:0]

bit[11:9]

9-bit FP read address

reserved, set to zero

FPRD

h

’

37

16

w

bit[8:0]

bit[11:9]

9-bit FP write address

reserved, set to zero

FPWR

h

’

38

16

w/r

bit[11:0]

FP data register, reading/writing to this

register will autoincrement the FP read/

write address. Only 16 bit of data are

transferred per I

2

C telegram.

FPDAT

BLACK LINE DETECTOR

h

’

12

16

w/r

read only register, do not write to this register!

after reading, LOWLIN and UPLIN are reset to 127 to start a new

measurement

bit[6:0]

number of lower black lines

bit[7]

always 0

bit[14:8]

number of upper black lines

bit[15]

0/1

normal/black picture

BLKLIN

LOWLIN

UPLIN

BLKPIC

PIN CIRCUITS

h

’

1F

16

w/r

INTLC & PORT pins:

bit[2:0]

0..7

output strength for INTLC & PORT Pins

(7 = tristate, 6 = weak ... 0 = strong)

reserved (set to 0)

pushpull/tristate for INTLC Pin

synchronization/no synchronization with

horizontal MSY for signal INTLC

reserved (set to 0)

bit[3]

bit[4]

bit[5]

0

0/1

0/1

bit[15:6]

0

0

0

TRPAD

SNCSTR

SNCDIS

VASYSEL

h

’

20

8

w/r

SYNC GENERATOR CONTROL:

bit[6:0]

0

bit[7]

0/1

reserved (set to 0)

positive/negative polarity for INTLC signal

0

SYNMODE

INTLCINV

PRIORITY BUS

h

’

24

8

w/r

priority bus ID register and control

bit [2:0]

0..7

bit [4:3]

0..3

bit [5]

0/1

bit [6]

0/1

priority ID, 0 highest

pad driver strength, 0 (strong) to 3 (weak)

reserved (set to 0)

source for prio request:

active video/clamp_to_1

disable/enable priority interface, if disabled

frontend is disconnected from priority bus!

bit [7]

0/1

0

0

0

0

0

PRIOMODE

PID

PRIOSTR

PIDSRC

PIDE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VDP3108PR | Consumer IC |

| VDSGLD_38.88 | TRANS PREBIASED PNP 200MW SOT23 |

| VDSL5100I | TVS 400W 43V UNIDIRECT SMA |

| VDSL5100 | TVS 400W 40V BIDIRECT SMA |

| VDSL6100I | TVS 400W 45V UNIDIRECT SMA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VDP5057 | 制造商:Panasonic Industrial Company 功能描述:BELT KIT |

| VDPC5S | 制造商:Speco 功能描述:SURFACE MOUNT CAMERA FOR VDP-5000 |

| VDPS0091 | 制造商:Panasonic Industrial Company 功能描述:ROLLER |

| VDPS0102 | 制造商:Panasonic Industrial Company 功能描述:ROLLER |

| VDPS0127 | 制造商:Panasonic Industrial Company 功能描述:ROLLER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。