- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361773 > W234 Clocks and Buffers PDF資料下載

參數(shù)資料

| 型號: | W234 |

| 英文描述: | Clocks and Buffers |

| 中文描述: | 時鐘和緩沖器 |

| 文件頁數(shù): | 5/14頁 |

| 文件大?。?/td> | 160K |

| 代理商: | W234 |

W234

Document #: 38-07232 Rev. *B

Page 5 of 14

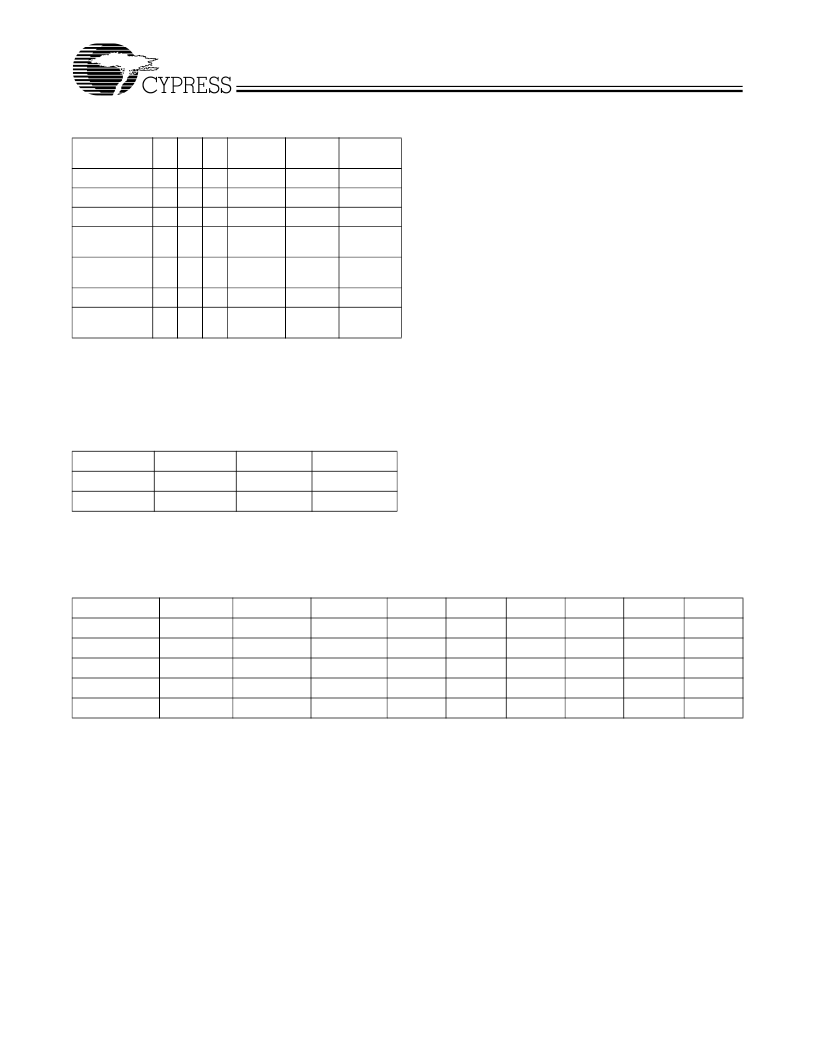

Table 4

shows the logic for selecting the Power-Down mode,

using the PWR_DWN# input signal. PWR_DWN# is active

LOW (enabled when 0). When PWR_DWN# is disabled, the

DRCG is in its normal mode. When PWR_DWN# is enabled,

the DRCG is put into a powered-off state, and the CLK and

CLK# outputs are three-stated.

Table of Frequencies and Gear Ratios

Table 5

shows several supported Pclk and Busclk frequencies,

the corresponding A and B dividers required in the DRCG PLL,

and the corresponding M and N dividers in the gear ratio logic.

The column Ratio gives the Gear Ratio as defined Pclk/Synclk

(same as M and N). The column F@PD gives the divided down

frequency (in MHz) at the Phase Detector (

φ

D

), where

F@PD = PCLK/M = SYNCLK/N.

State Transitions

The clock source has three fundamental operating states.

Figure 4

shows the state diagram with each transition labelled

A through H. Note that the clock source output may NOT be

glitch-free during state transitions.

Upon powering up the device, the device can enter any state,

depending on the settings of the control signals, PWR_DWN#

and STOP#.

In Power-Down mode, the clock source is powered down with

the control signal, PWR_DWN#, equal to 0. The control sig-

nals S0, S1 and S2 must be stable before power is applied to

the device, and can only be changed in Power-Down mode

(PWR_DWN#=0). The reference inputs, VDDIR and VDDIPD,

may remain on or may be grounded during the Power-Down

mode.

The control signals MULT0, MULT1, and MULT2 can be used

in two ways. If they are changed during Power-Down mode,

then the Power-Down transition timings determine the settling

time of the DRCG. However, the MULT0, MULT1, and MULT2

control signals can also be changed during Normal mode.

When the MULT control signals are

“

hot swapped

”

in this man-

ner, the MULT transition timings determine the settling time of

the DRCG.

Table 3. Bypass and Test Mode Selection

Mode

S0

S1

S2

By Pclk

(int.)

CLK

CLK#

Normal

0

0

0

Gnd

PAClk

PAClk#

Bypass

1

0

0

PLLClk

PLLClk

PLLClk#

Test

1

1

0

RefClk

RefClk

RefClk#

Vendor Test

A

0

0

1

-

-

-

Vendor Test

B

1

0

1

-

-

-

Reserved

1

1

1

-

-

-

Output Test

(OE)

0

1

X

-

Hi-Z

RefClk#

Table 4. PWR_DWN# Mode Selection

Mode

PWR_DWN#

Normal

Power-Down

CLK

PAClk

GND

CLK#

PAClk#

GND

1

0

Table 5. Frequencies, Dividers, and Gear Ratios

Pclk

Refclk

67

33

100

50

100

50

133

67

133

67

Busclk

267

300

400

267

400

Synclk

67

75

100

67

100

A

8

6

8

4

6

B

1

1

1

1

1

M

2

8

4

4

8

N

2

6

4

2

6

Ratio

1.0

1.33

1.0

2.0

1.33

F@PD

33

12.5

25

33

16.7

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| W23512-20 | x8 ROM (Mask Programmable) |

| W23512-25 | x8 ROM (Mask Programmable) |

| W23512H-20 | x8 ROM (Mask Programmable) |

| W23512H-25 | x8 ROM (Mask Programmable) |

| W2364-15 | x8 ROM (Mask Programmable) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| W234_02 | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:Dual Direct Rambus⑩ Clock Generator |

| W23-4700J | 制造商:TT Electronics / IRC 功能描述:RESISTOR WIREWOUND 470OHM 10W 5% 制造商:TT Electronics / IRC 功能描述:RESISTOR WIREWOUND, 470 OHM, 10W, 5%; Product Range:INTERNATIONAL RESISTIVE - W20 Series; Resistance:470ohm; Power Rating:10W; Resistance Tolerance: 5%; Resistor Case Style:Axial Leaded; Resistor Element Type:Ceramic; No. of Pins:2 ;RoHS Compliant: Yes |

| W234700JB | 功能描述:線繞電阻器 - 透孔 470ohm 10watt 5% RoHS:否 制造商:Bourns 電阻:10 Ohms 容差:5 % 功率額定值:7 W 溫度系數(shù):200 PPM / C 系列:FW 端接類型:Axial 工作溫度范圍:- 55 C to + 155 C 尺寸:9.5 mm Dia. x 26 mm L 封裝:Ammo 產(chǎn)品:Power Resistors Wirewound High Energy |

| W234700JBLF | 功能描述:線繞電阻器 - 透孔 470ohm 10watt 5% RoHS:否 制造商:Bourns 電阻:10 Ohms 容差:5 % 功率額定值:7 W 溫度系數(shù):200 PPM / C 系列:FW 端接類型:Axial 工作溫度范圍:- 55 C to + 155 C 尺寸:9.5 mm Dia. x 26 mm L 封裝:Ammo 產(chǎn)品:Power Resistors Wirewound High Energy |

| W234701JB | 功能描述:線繞電阻器 - 透孔 4.7K 10watt 5% RoHS:否 制造商:Bourns 電阻:10 Ohms 容差:5 % 功率額定值:7 W 溫度系數(shù):200 PPM / C 系列:FW 端接類型:Axial 工作溫度范圍:- 55 C to + 155 C 尺寸:9.5 mm Dia. x 26 mm L 封裝:Ammo 產(chǎn)品:Power Resistors Wirewound High Energy |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。