- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361795 > W89C880F LAN Hub Controller PDF資料下載

參數(shù)資料

| 型號: | W89C880F |

| 英文描述: | LAN Hub Controller |

| 中文描述: | 局域網(wǎng)集線器控制器 |

| 文件頁數(shù): | 37/72頁 |

| 文件大小: | 731K |

| 代理商: | W89C880F |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁當(dāng)前第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁

W89C840F

Publication Release Date:April 1997

Revision A1

- 37 -

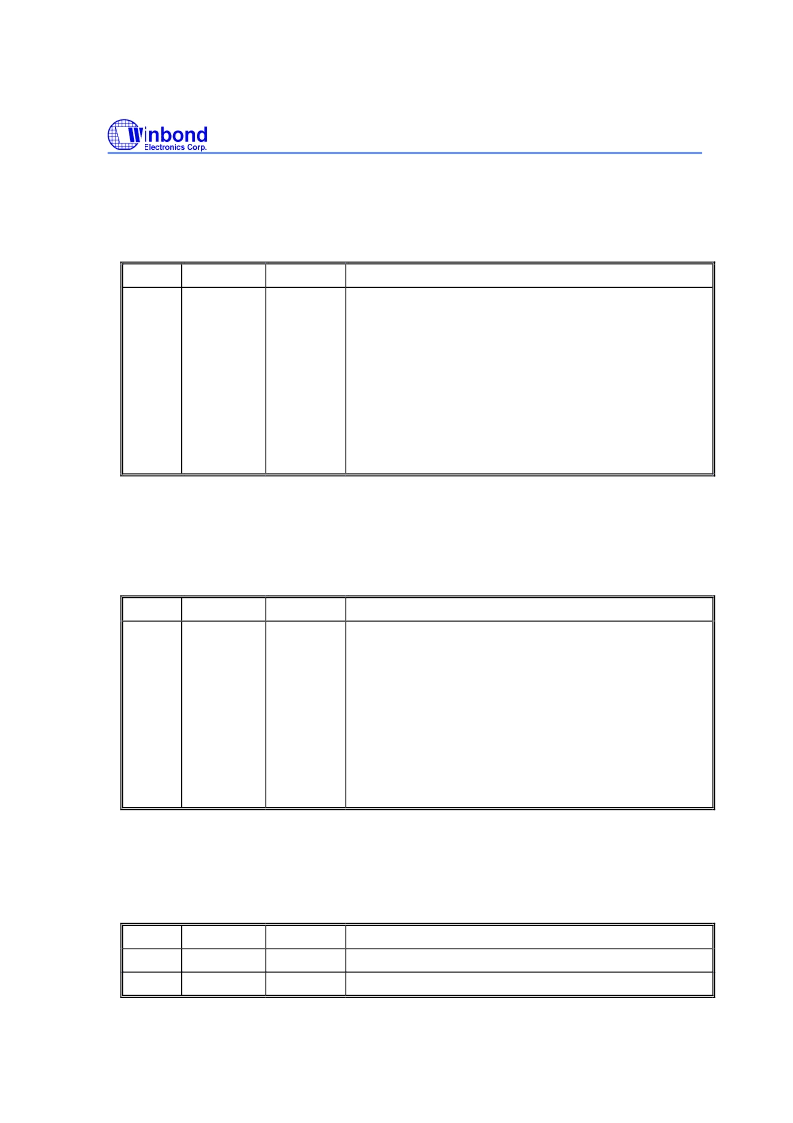

C04/CTSDR Transmit Start Demand Register

The register C04/CTSDR is used to request the W89C840F to do a transmission process.

Bit

Attribute

Bit name

Description

31:0

W

TSD

Transmit Start Demand

A write to this register will trigger the W89C840F‘s transmit

DMA to fetch the descriptor for progressing the transmission

operation when the W89C840F’s transmit DMA is staying at the

suspend state. Otherwise, the write operation will have no effect.

The W89C840F‘s transmit DMA will return to the suspend state

if no descriptor is available. Meanwhile, the bit 2 of C14/CISR

will be asserted to claim the transmit buffer unavailable

If there is any descriptor available, W89C840F will start to the

transmit process.

C08/CRSDR Receive Start Demand Register

The register C04/CTSDR is used to request the W89C840F to do a receive process.

Bit

Attribute

Bit name

Description

31:0

W

RSD

Receive Start Demand

A write to this register will trigger the W89C840F‘s receive

DMA to fetch the descriptor for progressing the receiving

operation when the W89C840F’s receive DMA is staying at the

suspend state. Otherwise, the write operation will have no effect.

The W89C840F‘s receive DMA will return to the suspend state

if no descriptor is available. Meanwhile, the bit 7 of C14/CISR

will be asserted to claim the receive buffer unavailable.

If there is any descriptor available, W89C840F will start to the

receive process and waiting for the incoming frames.

C0C/CRDLA Receive Descriptors List Addresses

The regi sters C0C/CRDLA defi ne

the start address of the receive descriptor list. It should be updated

only when the receive DMA state machine is staying at the stop state.

Bit

Attribute

Bit name

Description

31:2

R/W

SRL

Start of Receive List.

1:0

R/W

MBZ

Must be written as 0 for long word alignment.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| W89C840F | 100/10Mbps Ethernet Controller(100/10Mbps以太網(wǎng)控制器) |

| W89C92P | 10M CMOS Coaxial Transceiver |

| W89C940F | 10M PCI-Bus Ethernet Network Interface Controller |

| W91040 | |

| W91212 | Tone/Pulse Dialer With Redial Function(具有重?fù)芄δ艿囊纛l/脈沖撥號器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| W89C92 | 制造商:WINBOND 制造商全稱:Winbond 功能描述:PCMCIA ETHERNET NETWORK TWISTED PAIR INTERFACE CONTROLLER |

| W89C926 | 制造商:WINBOND 制造商全稱:Winbond 功能描述:PCMCIA ETHERNET NETWORK TWISTED PAIR INTERFACE CONTROLLER |

| W89C926F | 制造商:WINBOND 制造商全稱:Winbond 功能描述:10M PCMCIA Ethernet Network Interface Controller |

| W89C926PENTIC+ | 制造商:WINBOND 制造商全稱:Winbond 功能描述:PCMCIA ETHERNET NETWORK TWISTED PAIR INTERFACE CONTROLLER |

| W89C92P | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:10M CMOS Coaxial Transceiver |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。