- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19304 > XC2S300E-6PQ208C (Xilinx Inc)IC FPGA 1.8V 1536 CLB'S 208-PQFP PDF資料下載

參數(shù)資料

| 型號: | XC2S300E-6PQ208C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 26/108頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA 1.8V 1536 CLB'S 208-PQFP |

| 產(chǎn)品變化通告: | FPGA Family Discontinuation 18/Apr/2011 |

| 標(biāo)準(zhǔn)包裝: | 24 |

| 系列: | Spartan®-IIE |

| LAB/CLB數(shù): | 1536 |

| 邏輯元件/單元數(shù): | 6912 |

| RAM 位總計: | 65536 |

| 輸入/輸出數(shù): | 146 |

| 門數(shù): | 300000 |

| 電源電壓: | 1.71 V ~ 1.89 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 208-BFQFP |

| 供應(yīng)商設(shè)備封裝: | 208-PQFP(28x28) |

| 其它名稱: | 122-1211 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當(dāng)前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁

24

DS077-2 (v3.0) August 9, 2013

Product Specification

Spartan-IIE FPGA Family: Functional Description

R

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

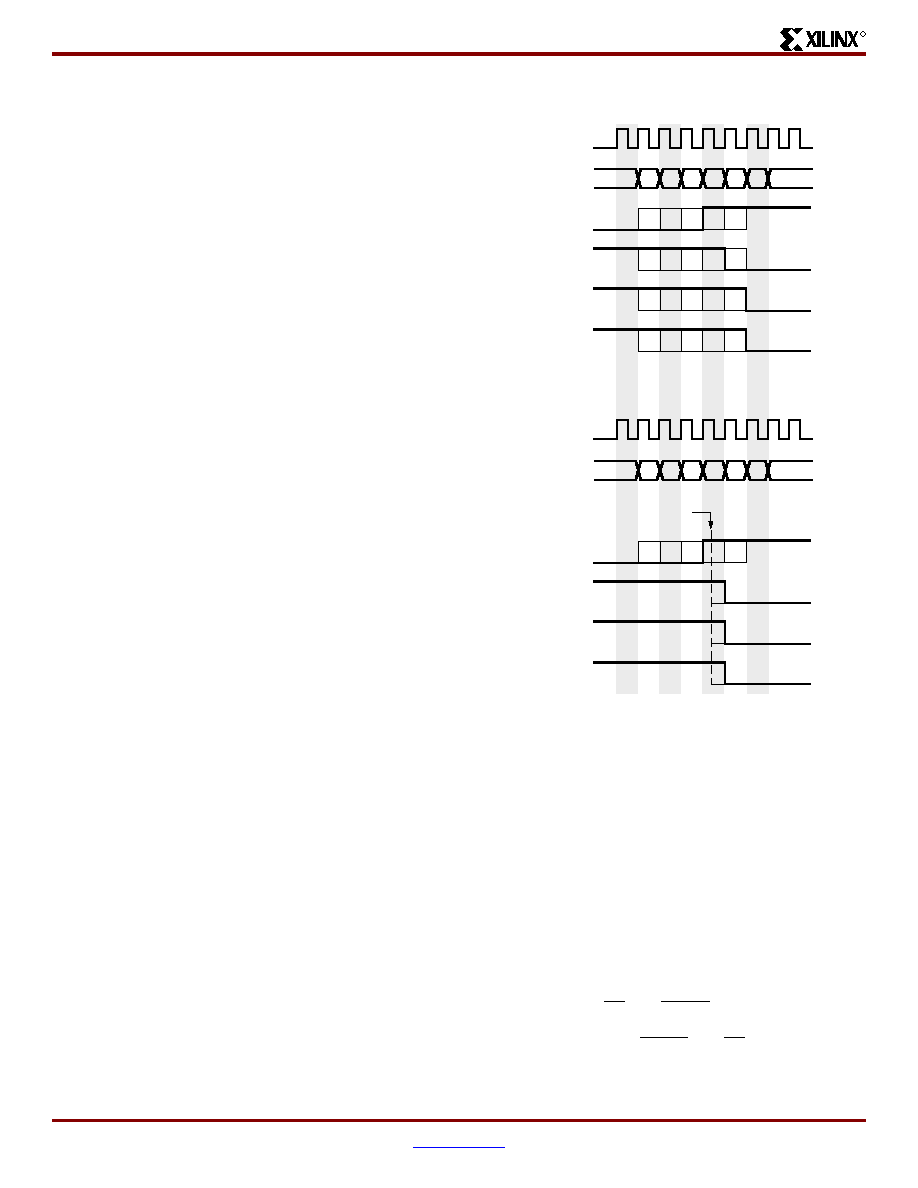

During start-up, the device performs four operations:

1.

The assertion of DONE. The failure of DONE to go High

may indicate the unsuccessful loading of configuration

data.

2.

The release of the Global Three State (GTS). This

activates all the I/Os to which signals are assigned. The

remaining I/Os stay in a high-impedance state with

internal weak pull-up resistors present.

3.

The release of the Global Set Reset (GSR). This allows

all flip-flops to change state.

4.

The assertion of Global Write Enable (GWE). This

allows all RAMs and flip-flops to change state.

By default, these operations are synchronized to CCLK.

The entire start-up sequence lasts eight cycles, called

C0-C7, after which the loaded design is fully functional. The

four operations can be selected to switch on any CCLK

cycle

C1-C6

through

settings

in

the

Xilinx

Development Software. The default timing for start-up is

shown in the top half of Figure 17; heavy lines show default

settings.

The default Start-up sequence is that one CCLK cycle after

DONE goes High, the global 3-state signal (GTS) is

released. This permits device outputs to turn on as neces-

sary.

One CCLK cycle later, the Global Set/Reset (GSR) and

Global Write Enable (GWE) signals are released. This per-

mits the internal storage elements to begin changing state

in response to the logic and the user clock.

The bottom half of Figure 17 shows another commonly

used

version

of

the

start-up

timing

known

as

Sync-to-DONE. This version makes the GTS, GSR, and

GWE events conditional upon the DONE pin going High.

This timing is important for a daisy chain of multiple FPGAs

in serial mode, since it ensures that all FPGAs go through

start-up together, after all their DONE pins have gone High.

Sync-to-DONE timing is selected by setting the GTS, GSR,

and GWE cycles to a value of DONE in the configuration

options. This causes these signals to transition one clock

cycle after DONE externally transitions High.

The sequence can also be paused at any stage until lock

has been achieved on any or all DLLs.

Serial Modes

There are two serial configuration modes. In Master Serial

mode, the FPGA controls the configuration process by driv-

ing CCLK as an output. In Slave Serial mode, the FPGA

passively receives CCLK as an input from an external agent

(e.g., a microprocessor, CPLD, or second FPGA in master

mode) that is controlling the configuration process. In both

modes, the FPGA is configured by loading one bit per CCLK

cycle. The MSB of each configuration data byte is always

written to the DIN pin first.

See Figure 18 for the sequence for loading data into the

Spartan-IIE FPGA serially. This is an expansion of the

"Load Configuration Data Frames" block in Figure 16,

page 23. Note that CS and WRITE are not normally used

during serial configuration. To ensure successful loading of

the FPGA, do not toggle WRITE with CS Low during serial

configuration.

Figure 17: Start-Up Waveforms

Start-up CLK

Default Cycles

Sync to DONE

01

2

3

4

5

6

7

01

DONE High

23

4

5

6

7

Phase

Start-up CLK

Phase

DONE

GTS

GSR

GWE

DS001_13_090600

DONE

GTS

GSR

GWE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| KA7815AE | IC REG LDO 15V 1A TO-220 |

| ESC43DRAS-S734 | CONN EDGECARD 86POS .100 R/A PCB |

| RBC13DRYN-S13 | CONN EDGECARD 26POS .100 EXTEND |

| MIC280-0BM6 TR | IC SUPERVISOR THERMAL SOT23-6 |

| MVAB120-12 | POWER SUPPLY 12V |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC2S300E-6PQ208I | 制造商:Xilinx 功能描述:FPGA SPARTAN-IIE 300K GATES 6912 CELLS 357MHZ 1.8V 208PQFP - Trays |

| XC2S300E-6PQG208C | 功能描述:IC SPARTAN-IIE FPGA 300K 208PQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-IIE 標(biāo)準(zhǔn)包裝:24 系列:ECP2 LAB/CLB數(shù):1500 邏輯元件/單元數(shù):12000 RAM 位總計:226304 輸入/輸出數(shù):131 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:208-BFQFP 供應(yīng)商設(shè)備封裝:208-PQFP(28x28) |

| XC2S300E-6PQG208I | 功能描述:IC SPARTAN-IIE FPGA 300K 208PQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-IIE 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XC2S300E-6TQ144C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE 1.8V FPGA Family |

| XC2S300E-6TQ144I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE 1.8V FPGA Family |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。