- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19303 > XC3S1000-4FTG256I (Xilinx Inc)SPARTAN-3A FPGA 1M STD 256-FTBGA PDF資料下載

參數(shù)資料

| 型號: | XC3S1000-4FTG256I |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 20/272頁 |

| 文件大?。?/td> | 0K |

| 描述: | SPARTAN-3A FPGA 1M STD 256-FTBGA |

| 產(chǎn)品培訓模塊: | Extended Spartan 3A FPGA Family |

| 標準包裝: | 90 |

| 系列: | Spartan®-3 |

| LAB/CLB數(shù): | 1920 |

| 邏輯元件/單元數(shù): | 17280 |

| RAM 位總計: | 442368 |

| 輸入/輸出數(shù): | 173 |

| 門數(shù): | 1000000 |

| 電源電壓: | 1.14 V ~ 1.26 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 100°C |

| 封裝/外殼: | 256-LBGA |

| 供應商設備封裝: | 256-FTBGA |

| 配用: | 122-1502-ND - KIT STARTER SPARTAN-3 PCI-E |

| 其它名稱: | 122-1709 XC3S1000-4FTG256I-ND |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁第219頁第220頁第221頁第222頁第223頁第224頁第225頁第226頁第227頁第228頁第229頁第230頁第231頁第232頁第233頁第234頁第235頁第236頁第237頁第238頁第239頁第240頁第241頁第242頁第243頁第244頁第245頁第246頁第247頁第248頁第249頁第250頁第251頁第252頁第253頁第254頁第255頁第256頁第257頁第258頁第259頁第260頁第261頁第262頁第263頁第264頁第265頁第266頁第267頁第268頁第269頁第270頁第271頁第272頁

Spartan-3 FPGA Family: Pinout Descriptions

DS099 (v3.1) June 27, 2013

Product Specification

116

The 1% precision impedance-matching resistor attached to the VRN_# pin controls the pull-down impedance of NMOS

transistor in the input or output buffer. Consequently, the VRN_# pin must connect to VCCO. The ‘N’ character in “VRN”

indicates that this pin controls the I/O buffer’s NMOS transistor impedance. The VRN_# pin is only used for split termination.

Each VRN or VRP reference input requires its own resistor. A single resistor cannot be shared between VRN or VRP pins

associated with different banks.

During configuration, these pins behave exactly like user-I/O pins. The associated DCI behavior is not active or valid until

after configuration completes.

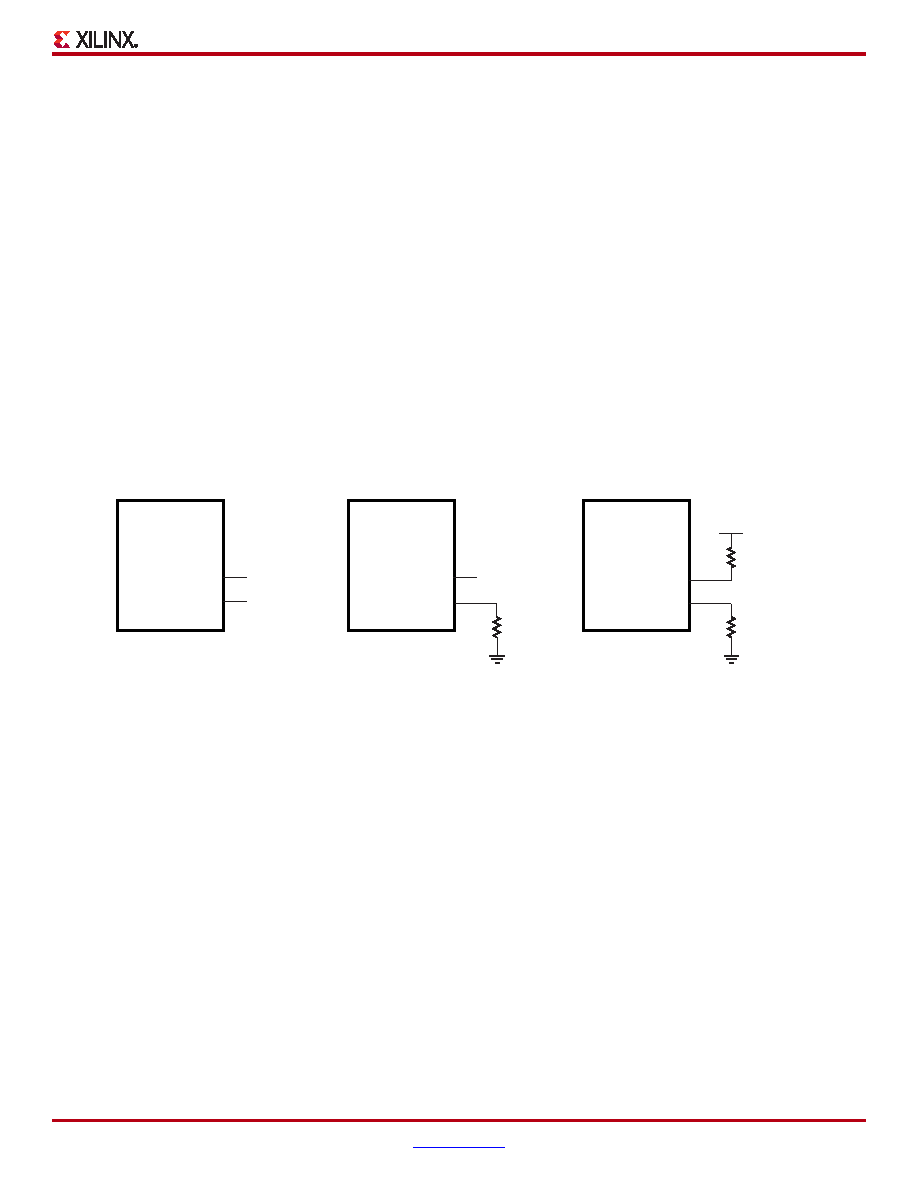

DCI Termination Types

If the I/O in an I/O bank do not use the DCI feature, then no external resistors are required and both the VRP_# and VRN_#

pins are available for user I/O, as shown in section [a] of Figure 42.

If the I/O standards within the associated I/O bank require single termination—such as GTL_DCI, GTLP_DCI, or

HSTL_III_DCI—then only the VRP_# signal connects to a 1% precision impedance-matching resistor, as shown in section

[b] of Figure 42. A resistor is not required for the VRN_# pin.

Finally, if the I/O standards with the associated I/O bank require split termination—such as HSTL_I_DCI, SSTL2_I_DCI,

SSTL2_II_DCI, or LVDS_25_DCI and LVDSEXT_25_DCI receivers—then both the VRP_# and VRN_# pins connect to

separate 1% precision impedance-matching resistors, as shown in section [c] of Figure 42. Neither pin is available for user

I/O.

GCLK: Global Clock Buffer Inputs or General-Purpose I/O Pins

These pins are user-I/O pins unless they specifically connect to one of the eight low-skew global clock buffers on the device,

specified using the IBUFG primitive.

There are eight GCLK pins per device and two each appear in the top-edge banks, Bank 0 and 1, and the bottom-edge

banks, Banks 4 and 5. See Figure 40 for a picture of bank labeling.

During configuration, these pins behave exactly like user-I/O pins.

Also see Global Clock Network, page 42.

CONFIG: Dedicated Configuration Pins

The dedicated configuration pins control the configuration process and are not available as user-I/O pins. Every package

has seven dedicated configuration pins. All CONFIG-type pins are powered by the +2.5V VCCAUX supply.

Also see Configuration, page 46.

X-Ref Target - Figure 42

Figure 42: DCI Termination Types

DS099-4_03_091910

VCCO

VRN

VRP

One of eight

I/O Banks

RREF (1%)

(c) Split termination

VRN

VRP

One of eight

I/O Banks

RREF (1%)

(b) Single termination

User I/O

One of eight

I/O Banks

(a) No termination

相關PDF資料 |

PDF描述 |

|---|---|

| EMC43DRXH-S734 | CONN EDGECARD 86POS DIP .100 SLD |

| 6-5174681-7 | CONN D-PLUG FEM SCKT 68POS VERT |

| NCV8509PDW26R2 | IC REG LDO 5V/2.6V 16SOIC |

| TACL475M003H | CAP TANT 4.7UF 3V 20% 0603 |

| GBC22DRTN-S13 | CONN EDGECARD 44POS .100 EXTEND |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| XC3S1000-4PQ208C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-3 FPGA |

| XC3S1000-4PQ208I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-3 FPGA |

| XC3S1000-4PQG208C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-3 FPGA Family: Complete Data Sheet |

| XC3S1000-4PQG208I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-3 FPGA Family: Complete Data Sheet |

| XC3S1000-4TQ144C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-3 FPGA |

發(fā)布緊急采購,3分鐘左右您將得到回復。