- 您現(xiàn)在的位置:買賣IC網 > PDF目錄16427 > XR17V258IV-0A-EVB (Exar Corporation)EVAL BOARD FOR XR17V258 144LQFP PDF資料下載

參數(shù)資料

| 型號: | XR17V258IV-0A-EVB |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 4/69頁 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR XR17V258 144LQFP |

| 標準包裝: | 1 |

| 系列: | * |

第1頁第2頁第3頁當前第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁

XR17V258

12

66MHZ PCI BUS OCTAL UART WITH POWER MANAGEMENT SUPPORT

REV. 1.0.2

NOTE: RWR=Read/Write from AD[31:0]. RO= Read Only. RWC=Read/Write-Clear.

1.2.1

Power States and Power State Transitions of the V258

The XR17V258 supports D0, D3hot and D3cold power states and is capable of generating the PME# signal

from the D3hot state. The following paragraphs describe these power states and Figure 4 shows the power

state transitions of the V258.

D0 STATE

The XR17V258 must be placed in the D0 state before being used in a system. The D0 state represents two

states - D0 Uninitalized and D0 Active. Upon entering D0 from power up or transition from D3hot, the V258 will

be in the D0 Uninitialized state. Once initialized by the system software, the V258 will enter the D0 Active state.

In the D0 Active state, the V258 is fully functional and will respond to all PCI bus transactions as well as issue

interrupts (INTA#). The system software can program the V258 to enter the D3hot state from the D0 state.

D3

HOT STATE

The V258 enters the D3hot state when the system software programs the V258 from D0 to D3hot, via PMCSR

bits [1:0]. In this state, the V258 will not be fully functional. The V258 will respond only to PCI configuration

space accesses, if a PCI clock is provided and will not respond to PCI memory accesses nor will it issue

interrupts. However, the V258 will continue to receive data and the automatic software and hardware flow

control, if enabled, will continue to function normally. While in the D3hot state, the V258 asserts the PME#

(Power Management Event) signal, if enabled by setting PME_Enable bit (bit-8 of PMCSR), upon one of the

following events:

■ RX pin of any of the channels goes LOW (START bit detected), or

■ Any of the delta bits of modem inputs (MSR register bits [3:0]) is set in any of the 8 channels (see

The V258 also sets the PME_Status bit when such an event occurs, regardless of whether the PME_Enable bit

is set or not. The system software can reset the PME_Status bit by writing a ’1’ to it. When the system software

programs the V258 from D3hot to D0, typically in response to the PME# signal, the V258 enters the D0 Active

state and will retain all the values of its internal registers. The V258 will keep its PCI signal drivers disabled for

the duration of the D3hot to D0 Uninitialized state transition. The V258 saves the PME context (configuration

registers and functional state information) in the D3hot state.

Note: The V258 has a sleep mode which keeps the power consumption to a minimum (see Sleep Mode

description on page 24). This is independent of the power state the V258 is in. The user can optionally place

the V258 in sleep mode (via the software driver) in the Active D0 state anytime or specifically when the system

software commands the V258 to enter the D3hot state. The crystal oscillator shuts down when the conditions

given in Sleep Mode section on page 24 are satisfied, and re-starts when one of the events as described in the

same section occurs. Upon re-starting, the oscillator may take a long time to settle. This time may be more

than 20ms which is the maximum wait time guaranteed by the system software before resuming normal PCI

bus transactions in the Active D0 state. Therefore, there may be data errors if the V258 is commanded to

transmit data before the oscillator is ready. It is recommended not to use sleep mode while in the D3hot

state for this reason.

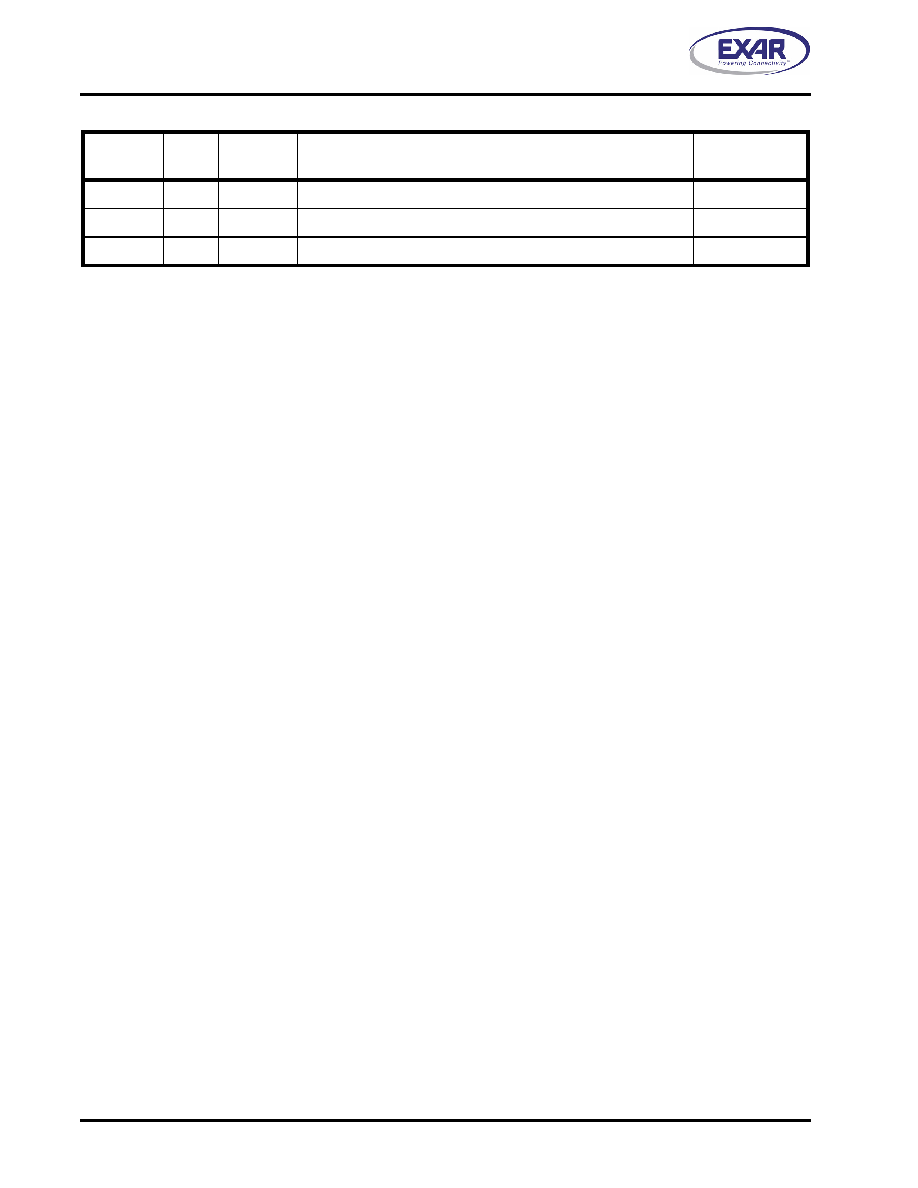

8

RWR

PME_Enable

0b

7:2

RO

Reserved

000000b

1:0

RWR

PowerState

00b

TABLE 2: POWER MANAGEMENT REGISTERS

ADDRESS

OFFSET

BITS

TYPE

DESCRIPTION

RESET VALUE

(HEX OR BINARY)

相關PDF資料 |

PDF描述 |

|---|---|

| GCC10DRYN-S734 | CONN EDGECARD 20POS DIP .100 SLD |

| VI-B1Y-EV | CONVERTER MOD DC/DC 3.3V 99W |

| 155880-000 | SOLDER SLEEVE 11MM DIA SHIELD |

| VI-2VR-EX | CONVERTER MOD DC/DC 7.5V 75W |

| VI-2VP-EX | CONVERTER MOD DC/DC 13.8V 75W |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| XR17V258IVF | 制造商:Exar Corporation 功能描述: |

| XR17V258IV-F | 功能描述:UART 接口集成電路 66MHz Octal PCI UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR17V258IVTR-F | 功能描述:UART 接口集成電路 66MHz Octal PCI UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR17V352 | 制造商:EXAR 制造商全稱:EXAR 功能描述:HIGH PERFORMANCE DUAL PCI EXPRESS UART |

| XR17V352IB-0A-EVB | 功能描述:界面開發(fā)工具 Eval Board for XR17V352IB Series RoHS:否 制造商:Bourns 產品:Evaluation Boards 類型:RS-485 工具用于評估:ADM3485E 接口類型:RS-485 工作電源電壓:3.3 V |

發(fā)布緊急采購,3分鐘左右您將得到回復。