- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376462 > XRT75L00DIV (EXAR CORP) E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER PDF資料下載

參數(shù)資料

| 型號: | XRT75L00DIV |

| 廠商: | EXAR CORP |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER |

| 中文描述: | DATACOM, PCM TRANSCEIVER, PQFP52 |

| 封裝: | 10 X 10 MM, TQFP-52 |

| 文件頁數(shù): | 39/92頁 |

| 文件大小: | 894K |

| 代理商: | XRT75L00DIV |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁當前第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁

XRT75L00D

REV. 1.0.2

E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER

34

6.2

Jitter Transfer function is defined as the ratio of jitter on the output relative to the jitter applied on the input

versus frequency.

There are two distinct characteristics in jitter transfer: jitter gain (jitter peaking) defined as the highest ratio

above 0 dB; and jitter transfer bandwidth.The overall jitter transfer bandwidth is controller by a low bandwidth

loop,which is part of the XRT75L00D.

The jitter transfer function is a ratio between the jitter output and jitter input for a component, or system often

expressed in dB. A negative dB jitter transfer indicates the element removed jitter. A positive dB jitter transfer

indicates the element added jitter.A zero dB jitter transfer indicates the element had no effect on jitter.

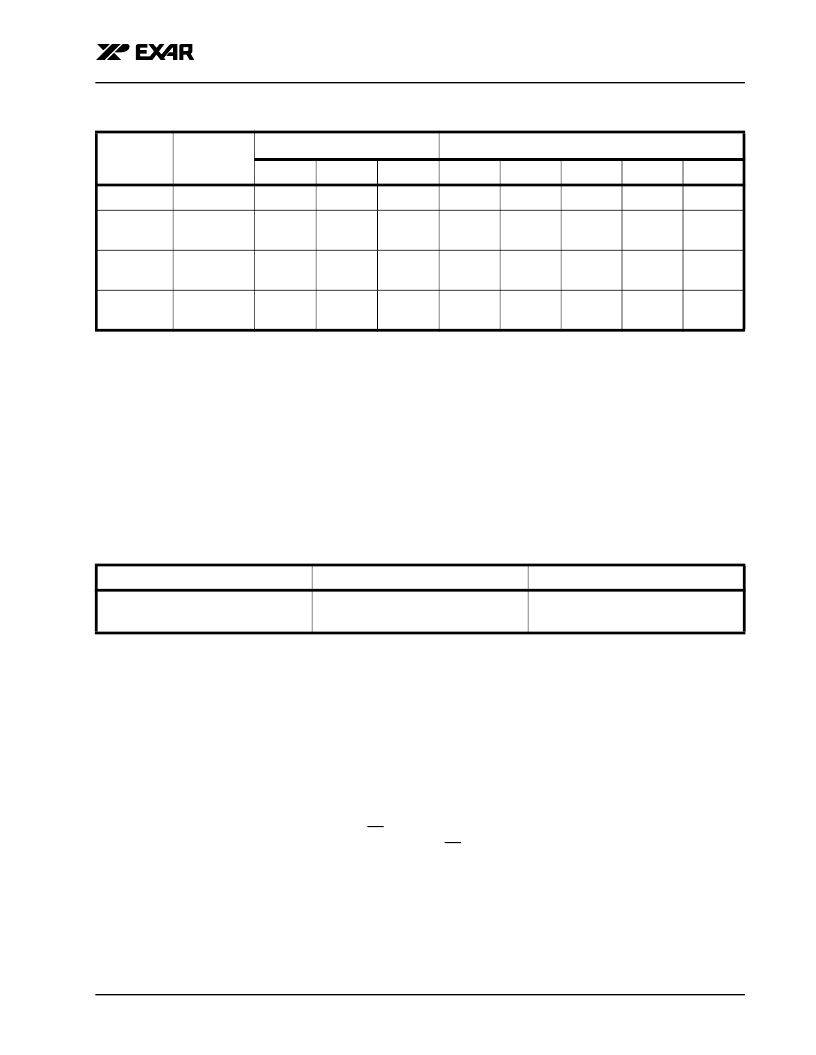

Table 12 shows the jitter transfer characteristics and/or jitter attenuation specifications for various data rates:

J

ITTER

T

RANSFER

- R

ECEIVER

/T

RANSMITTER

:

The XRT75L00D meets the above Jitter Specifications.

6.3

J

ITTER

G

ENERATION

:

Jitter Generation is defined as the process whereby jitter appears at the output port of the digital equipment in

the absence of applied input jitter. Jitter Generation is measured by sending jitter free data to the clock and

data recovery circuit and measuring the amount of jitter on the output clock or the re-timed data. Since this is

essentially a noise measurement, it requires a definition of bandwidth to be meaningful. The bandwidth is set

according to the data rate. In general, the jitter is measured over a band of frequencies.

6.4

Jitter Attenuator:

An advanced crystal-less jitter attenuator is included in the XRT75L00D. The jitter attenuator uses the internal

reference clock.

In Host mode, by clearing or setting the JATx/Rx bit in the control register selects the jitter attenuator either in

the Receive or Transmit path. In Hardware mode, JATx/Rx pin selects the jitter attenuator in Receive or

Transmit path.

The FIFO is either a 16-bit, 32-bit or 128-bit register. In Host mode, the bits JA0 and JA1can be set to

appropriate combination to select the different FIFO sizes or to disable the jitter attenuator. In Hardware mode,

appropriate setting of the pins JA0 and JA1 selects the different FIFO sizes or disable the jitter attenuator. Data

is clocked into the FIFO with the associated clock signal (TxClk or RxClk) and clocked out of the FIFO with the

dejittered clock. When the FIFO is within two bits of overflowing or underflowing, the FIFO limit status bit, FL is

set to “1” in the Alarm status register. Reading this bit clears the FIFO and resets the bit into default state.

T

ABLE

11: J

ITTER

A

MPLITUDE

VERSUS

M

ODULATION

F

REQUENCY

(J

ITTER

T

OLERANCE

)

B

IT

R

ATE

(

KB

/

S

)

S

TANDARD

I

NPUT

J

ITTER

A

MPLITUDE

(UI

P

-

P

)

M

ODULATION

F

REQUENCY

A1

A2

A3

F

1(H

Z

)

F

2(H

Z

)

F

3(

K

H

Z

)

F

4(

K

H

Z

)

F

5(

K

H

Z

)

34368

ITU-T G.823

1.5

0.15

-

100

1000

10

800

-

44736

GR-499

CORE Cat I

5

0.1

-

10

2.3k

60

300

-

44736

GR-499

CORE Cat II

10

0.3

-

10

669

22.3

300

-

51840

GR-253

CORE Cat II

15

1.5

0.15

10

30

300

2

20

T

ABLE

12: J

ITTER

T

RANSFER

S

PECIFICATIONS

E3

DS3

STS-1

ETSI TBR-24

GR-499 CORE section 7.3.2

Category I and Category II

GR-253 CORE section 5.6.2.1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT75L02 | TWO CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER |

| XRT75L02IV | TWO CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER |

| XRT75L03D | THREE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER |

| XRT75L04D | FOUR CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER |

| XRT75L04DIV | FOUR CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT75L00DIV-F | 功能描述:外圍驅(qū)動器與原件 - PCI 1-Ch DS3, E3, SONET RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| XRT75L00DIVTR | 功能描述:時鐘合成器/抖動清除器 3.3V 1 CH E3/DS3/STS W/SONET DE-SYNCH RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| XRT75L00DIVTR-F | 功能描述:時鐘合成器/抖動清除器 3.3V 1 CH E3/DS3/STS W/SONET DE-SYNCH RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| XRT75L00ES | 功能描述:時鐘合成器/抖動清除器 1CH T3/E3/STS1 LIU+JA 3.3V RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| XRT75L00IV | 功能描述:外圍驅(qū)動器與原件 - PCI 3.3V 1 CH E3/DS3/STS W/JITTER ATTEN RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復。