- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376462 > XRT75R12D (Exar Corporation) TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER PDF資料下載

參數(shù)資料

| 型號: | XRT75R12D |

| 廠商: | Exar Corporation |

| 英文描述: | TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER |

| 中文描述: | 第十二章通道E3/DS3/STS-1線路接口單元與SONET DESYNCHRONIZER |

| 文件頁數(shù): | 96/131頁 |

| 文件大小: | 717K |

| 代理商: | XRT75R12D |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁當前第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁

XRT75R12D

REV. P1.0.1

TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER

PRELIMINARY

91

Although the role of the H1, H2 and H3 bytes will be discussed in much greater detail in “Section 8.3, Jitter/

Wander due to Pointer Adjustments” on page 98. For now, we will simply state that the role of these bytes is

two-fold.

To permit a given PTE (Path Terminating Equipment) that is receiving an STS-1 data to be able to locate the

STS-1 SPE (Synchronous Payload Envelope) within the Envelope Capacity of this incoming STS-1 data

stream and,

To inform a given PTE whenever Pointer Adjustment and NDF (New Data Flag) events occur within the

incoming STS-1 data-stream.

8.2.1.1.2

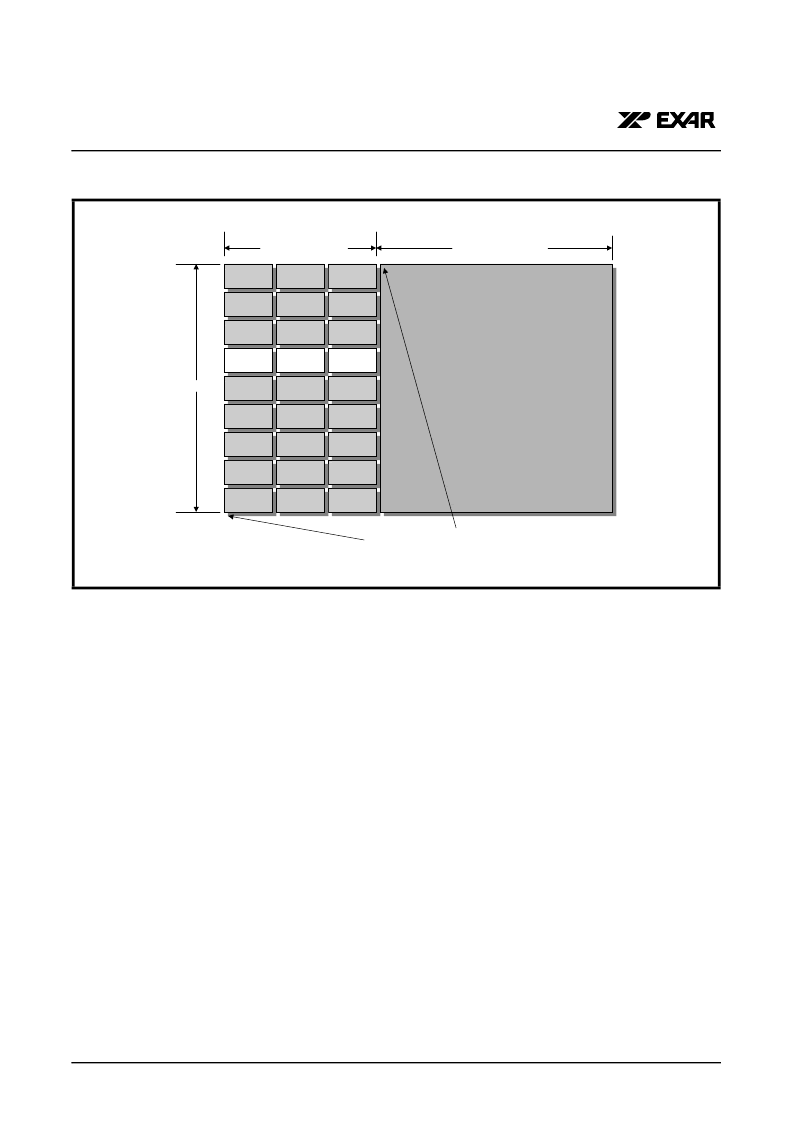

The Envelope Capacity Bytes within an STS-1 Frame

In general, the Envelope Capacity Bytes are any bytes (within an STS-1 frame) that exist outside of the TOH

bytes. In short, the Envelope Capacity contains the STS-1 SPE (Synchronous Payload Envelope). In fact,

every single byte that exists within the Envelope Capacity also exists within the STS-1 SPE. The only

difference that exists between the "Envelope Capacity" as defined in Figure 40 and Figure 41 above and the

STS-1 SPE is that the Envelope Capacity is aligned with the STS-1 framing boundaries and the TOH bytes;

whereas the STS-1 SPE is NOT aligned with the STS-1 framing boundaries, nor the TOH bytes.

The STS-1 SPE is an "87 byte column x 9 row" data-structure (which is the exact same size as is the Envelope

Capacity) that is permitted to "float" within the "Envelope Capacity". As a consequence, the STS-1 SPE (within

an STS-1 data-stream) will typically straddle across an STS-1 frame boundary.

8.2.1.1.3

The Byte Structure of the STS-1 SPE

As mentioned above, the STS-1 SPE is an 87 byte column x 9 row structure. The very first column within the

STS-1 SPE consists of some overhead bytes which are known as the "Path Overhead" (or POH) bytes. The

remaining portions of the STS-1 SPE is available for "user" data. The Byte Structure of the STS-1 SPE is

presented below in Figure 42.

F

IGURE

41. T

HE

B

YTE

-F

ORMAT

OF

THE

TOH

WITHIN

AN

STS-1 F

RAME

A1

B1

D1

H1

B2

D4

D7

S1

D10

C1

F1

D3

H3

K2

D6

D9

E2

D12

A2

E1

D2

H2

K1

D5

D8

M0

D11

Bytes

Envelope Capacity

3 Byte Columns

87 Byte Columns

9 Rows

The TOH Bytes

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT75R12DIB | TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER |

| XRT75R12 | TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

| XRT75R12IB | TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

| XRT75VL00 | E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

| XRT75VL00IV | E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT75R12D_06 | 制造商:EXAR 制造商全稱:EXAR 功能描述:TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET |

| XRT75R12D_07 | 制造商:EXAR 制造商全稱:EXAR 功能描述:TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET |

| XRT75R12DES | 功能描述:時鐘合成器/抖動清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| XRT75R12DIB | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 12CH E3/DS3/STS W/JITTER R3 TECH RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| XRT75R12DIB-F | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 12 Channel 3.3V-5V temp -45 to 85C RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復。