- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376462 > XRT79L74IB (EXAR CORP) 4 - CHANNEL DS3/E3 ATM UNI/PPP COMBO IC PDF資料下載

參數(shù)資料

| 型號: | XRT79L74IB |

| 廠商: | EXAR CORP |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | 4 - CHANNEL DS3/E3 ATM UNI/PPP COMBO IC |

| 中文描述: | ATM NETWORK INTERFACE, PBGA456 |

| 封裝: | 27 X 27 MM, 1 MM PITCH, PLASTIC, BGA-456 |

| 文件頁數(shù): | 38/70頁 |

| 文件大小: | 547K |

| 代理商: | XRT79L74IB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁當(dāng)前第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁

XRT79L74

REV. P1.0.0

PRELIMINARY

4 - CHANNEL DS3/E3 ATM UNI/PPP COMBO IC

36

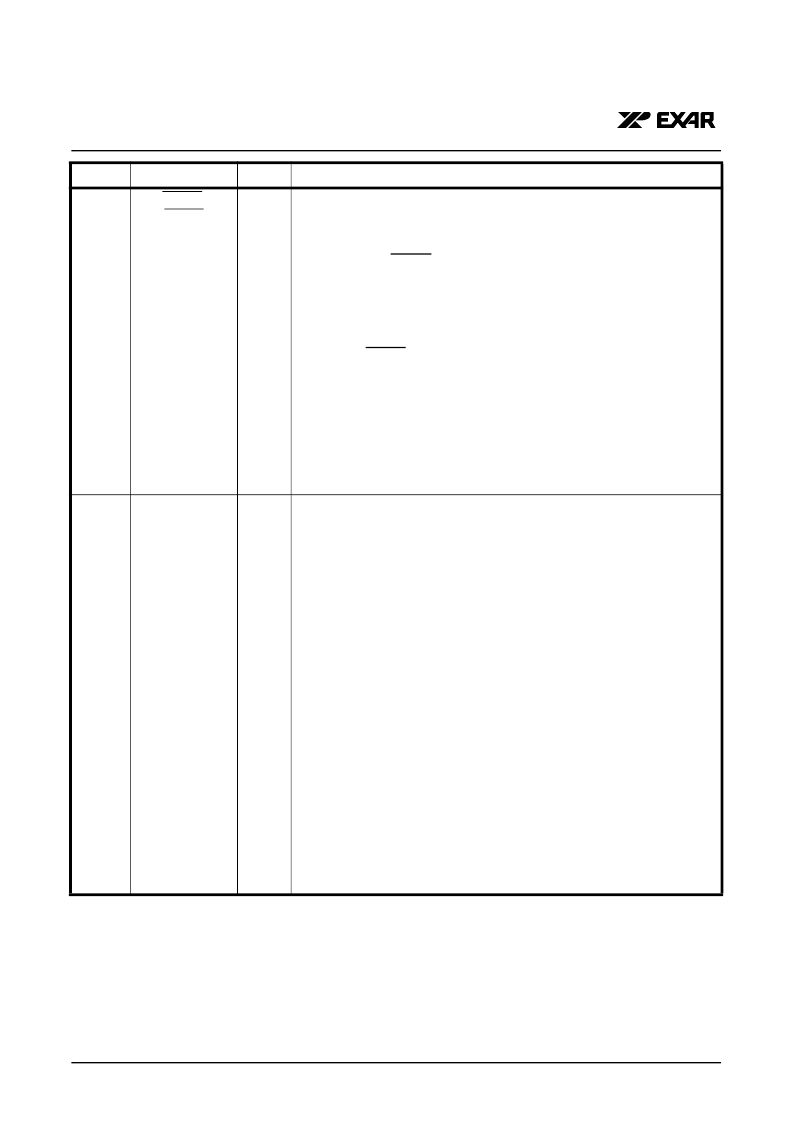

C16

RxUEN/

RxPEN

I

Receive UTOPIA Interface - Output Enable/Receive POS-PHY Interface -

Output Enable:

The function of this output pin depends upon whether the XRT79L74 has been

configured to operate in the ATM UNI or PPP mode.

ATM UNI Mode - RxUEN:

This active-low input signal is used to control the drivers of the Receive UTOPIA

Data Bus. When this signal is "High" (negated) then the Receive UTOPIA Data

Bus is tri-stated. When this signal is asserted, then the contents of the byte or

word that is at the front of the RxFIFO will be popped and placed on the Receive

UTOPIA Data bus on the very next rising edge of RxUClk.

PPP Mode - RxPEN:

This active-low input signal is used to control the drivers of the Receive POS-

PHY Data Bus. When this signal is "High" (negated) then the Receive POS-

PHY Data Bus is tri-stated. When this signal is asserted, then the contents of

the byte or word that is at the front of the RxFIFO will be popped and placed on

the Receive POS-PHY Data bus on the very next rising edge of RxPClk.

N

OTE

:

The user should tie these input pins to GND, if he/she intends to operate

the XRT79L74 device in either the Clear-Channel Framer or High-

Speed HDLC Controller Modes.

A16

RxUSoC/

RxPSOP/RxP-

SOC

O

Receive UTOPIA Interface - Start of Cell Indicator/Receive POS-PHY Inter-

face - Start of Packet Indicator:

The function of this output pin depends upon whether the XRT79L74 has been

configured to operate in the ATM UNI or in the PPP Mode.

ATM UNI Mode - RxUSoC:

This output pin allows the ATM Layer Processor to determine the boundaries of

the ATM cells that are output via the Receive UTOPIA Data bus. The Receive

UTOPIA Interface block will assert this signal when the first byte (or word) of a

new cell is present on the Receive UTOPIA Data Bus; RxUData[15:0].

PPP Mode - RxPSOP:

This output pin allows the Link Layer Processor to determine the boundaries of

the PPP packets that are output via the Receive POS-PHY Data Bus. The

Receive POS-PHY Interface block will assert this signal when the first byte (or

word) of a new packet is present on the Receive POS-PHY Data Bus, RxP-

Data[15:0].

PPP Chunk Mode - RxPSOC - Receive Start of Chunk Indicator Output

(Chunk Mode):

If the XRT79L74 device has been configured to operate in the "Chunk Mode,

then the Receive POS-PHY Interface block will pulse this output pin "high" coin-

cident to whenever it outputs the very first byte (or 16-bit word) of a given Chunk

onto the Receive POS-PHY Data Bus (RxPData[15:0]) output pins. The

Receive POS-PHY Interface block will keep this output pin "low" at all other

times.

N

OTE

:

In the "PPP Chunk" Mode, the RxPSOF output pin will function as the

"Start of Packet" Output Indicator pin.

P

IN

#

N

AME

TYPE

D

ESCRIPTION

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT8000ID | Clock Synchronizer/Adapter for Communications |

| XRT8000 | Clock Synchronizer/Adapter for Communications(用于通訊的時鐘同步設(shè)備/調(diào)整器) |

| XRT8001 | WAN Clock for T1 and E1 Systems |

| XRT8001ID | WAN Clock for T1 and E1 Systems |

| XRT8001IP | WAN Clock for T1 and E1 Systems |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT8000 | 制造商:EXAR 制造商全稱:EXAR 功能描述:Clock Synchronizer/Adapter for Communications |

| XRT8000_06 | 制造商:EXAR 制造商全稱:EXAR 功能描述:Clock Synchronizer/Adapter for Communications |

| XRT8000D | 制造商:EXAR 制造商全稱:EXAR 功能描述:CLOCK SYNCHRONIZER/ADAPTER FOR COMMUNICATIONS |

| XRT8000ES | 功能描述:鎖相環(huán) - PLL WAN CLOCK RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| XRT8000ID | 制造商:EXAR 制造商全稱:EXAR 功能描述:Clock Synchronizer/Adapter for Communications |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。