- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376464 > XRT91L82 (Exar Corporation) 2.488/2.666 GBPS STS-48/STM-16 SONET/SDH TRANSCEIVER PDF資料下載

參數(shù)資料

| 型號: | XRT91L82 |

| 廠商: | Exar Corporation |

| 英文描述: | 2.488/2.666 GBPS STS-48/STM-16 SONET/SDH TRANSCEIVER |

| 中文描述: | 2.488/2.666 Gbps的STS-48/STM-16的SONET / SDH收發(fā)器 |

| 文件頁數(shù): | 25/59頁 |

| 文件大小: | 414K |

| 代理商: | XRT91L82 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當(dāng)前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁

xr

REV. P1.0.5

PRELIMINARY

2.488/2.666 GBPS STS-48/STM-16 SONET/SDH TRANSCEIVER

XRT91L82

22

2.7

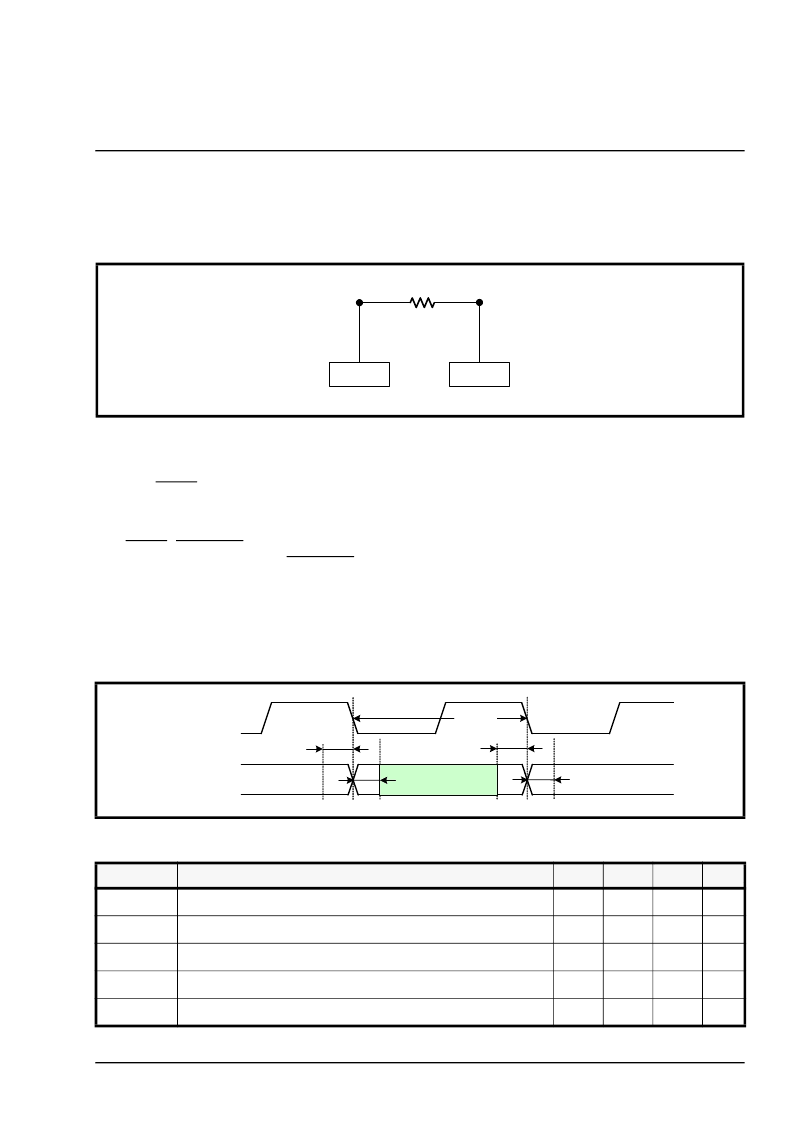

When operating the 16-bit Differential bus in LVDS mode, a 402

external resistor is needed across XRES1P

and XRES1N to properly bias the RXDO[15:0]P/N and RXPCLKOP/N pins. Figure 8 shows the proper biasing

resistor installed.

Receive Parallel Interface LVDS Operation

2.8

The parallel receiver data outputs are automatically pulled "Low" during a LOSD condition to prevent data

chattering. However, the user must select the proper SDEXT polarity for the optical module used. In addition,

by pulling DISRD "Low", the receiver data outputs will be muted asynchronously or forced to a logic state of "0"

regardless of the data input stream.

2.9

Parallel Receive Clock Output Disable

Like DISRD, DISRDCLK is used to mute the parallel receiver clock output RXPCLKOP/N regardless of the

data input stream. By pulling DISRDCLK "Low", the receiver clock output will be asynchronously muted

whenever desired.

2.10

Receive Parallel Data Output Timing

The receive parallel data output from the STS-48/STM-16 receiver will adhere to the setup and hold times

shown in Figure 9 and Table 7.

F

IGURE

9. R

ECEIVE

P

ARALLEL

O

UTPUT

T

IMING

Parallel Receive Data Output Disable/Mute Upon LOSD

T

ABLE

7: R

ECEIVE

P

ARALLEL

D

ATA

AND

C

LOCK

O

UTPUT

T

IMING

S

PECIFICATIONS

F

IGURE

8. LVDS

EXTERNAL

BIASING

RESISTORS

S

YMBOL

P

ARAMETER

M

IN

T

YP

M

AX

U

NITS

t

RXPCLKO

Receive parallel clock output period (155.52 MHz non-FEC rate)

6.43

ns

t

RXPCLKO

Receive parallel clock output period (166.63 MHz FEC rate)

6.00

ns

t

RX_INV

RXPCLKOP/N "Low" to data invalid window

1000

ps

t

RX_DEL

RXPCLKOP/N "Low" to data delay

900

ps

RX

DUTY

RXPCLKOP/N Duty Cycle

45

55

%

XRES1N

XRES1P

402

+/- 1 % tolerance

pin E14

pin F14

RXPCLKOP/N

RXDO[15:0]P/N

t

RX_INV

t

RXPCLKO

t

RX_INV

t

RX_DEL

SAMPLE WINDOW

t

RX_DEL

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT91L82IB | 2.488/2.666 GBPS STS-48/STM-16 SONET/SDH TRANSCEIVER |

| XRT94L31_07 | 3-CHANNEL DS3/E3/STS-1 TO STS-3/STM-1 MAPPER IC |

| XRT94L31 | 3-CHANNEL DS3/E3/STS-1 TO STS-3/STM-1 MAPPER |

| XRT94L31IB | 3-CHANNEL DS3/E3/STS-1 TO STS-3/STM-1 MAPPER |

| XRT94L43A | SONET/SDH OC-12 TO 12XDS3/E3 MAPPER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT91L82ES | 功能描述:總線收發(fā)器 Transceiver RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時(shí)間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| XRT91L82IB | 功能描述:總線收發(fā)器 Transceiver RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時(shí)間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| XRT91L82IB-F | 功能描述:總線收發(fā)器 Transceiver RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時(shí)間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| XRT94L31 | 制造商:EXAR 制造商全稱:EXAR 功能描述:3-CHANNEL DS3/E3/STS-1 TO STS-3/STM-1 MAPPER IC |

| XRT94L31_07 | 制造商:EXAR 制造商全稱:EXAR 功能描述:3-CHANNEL DS3/E3/STS-1 TO STS-3/STM-1 MAPPER IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。