- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373761 > Z80L182 (ZiLOG, Inc.) CAP .0001UF 50V POLYPROPYLENE PDF資料下載

參數(shù)資料

| 型號: | Z80L182 |

| 廠商: | ZiLOG, Inc. |

| 英文描述: | CAP .0001UF 50V POLYPROPYLENE |

| 中文描述: | ZiLOG的智能外設(shè)控制器(郵編⑩) |

| 文件頁數(shù): | 69/109頁 |

| 文件大?。?/td> | 738K |

| 代理商: | Z80L182 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁當(dāng)前第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁

3-69

Z80182/Z8L182

Z

ILOG

I

NTELLIGENT

P

ERIPHERAL

P R E L I M I N A R Y

Zilog

DS971820600

16550 MIMIC REGISTERS

The Z80182/Z8L182 contains the following set of registers

for interfacing with the PC/XT/AT.

– Receive Buffer Register

– Transmit Holding Register

– Interrupt Enable Register

– Interrupt Identification Register

– FIFO Control Register

– Line Control Register

– Modem Control Register

– Line Status Register

– Modem Status Register

– Scratch Register

– Divisor Latch Least/Most Significant Bytes

– FIFO Control Register

These registers emulate the 16550 UART and enable the

PC/XT/AT to interface with them as with an actual 16550

UART. This allows the Z80182/Z8L182 to be software

compatible with existing modem software.

0

0

0

0

0

0

0

0

D7

D6

D5

D4

D3

D2

D1

D0

Receive Buffer Register

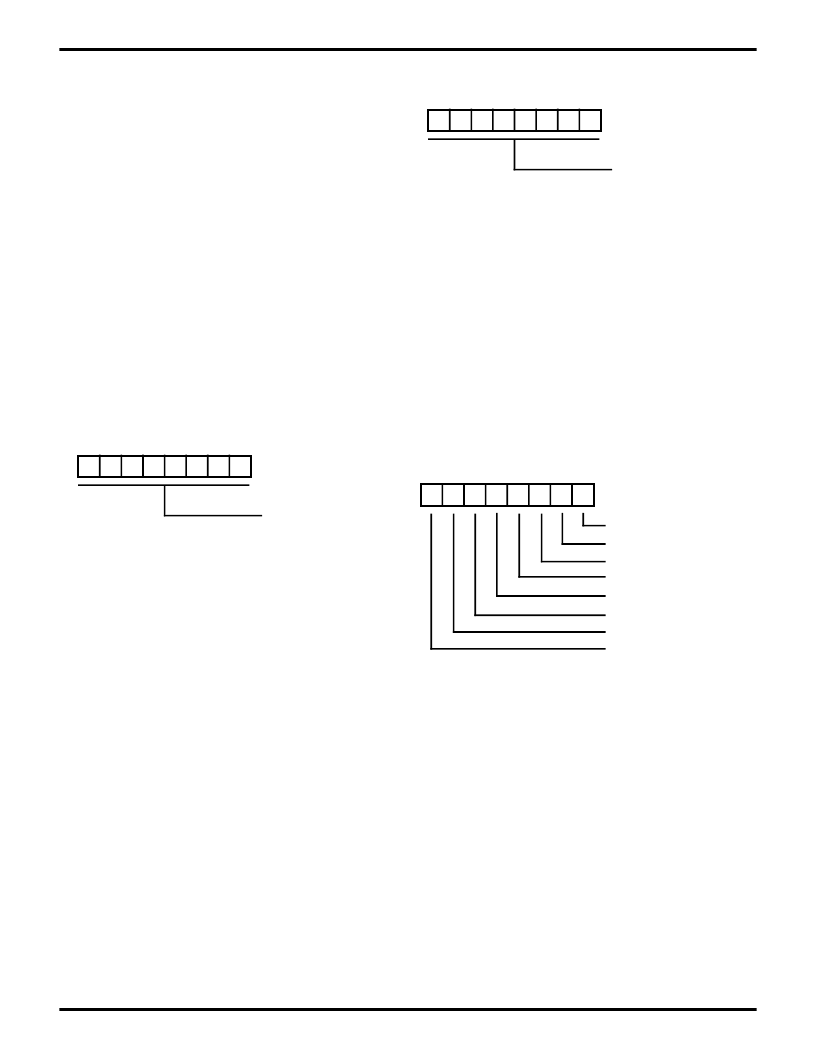

Figure 69. Receive Buffer Register

(PC Read Only, Address 00H, DLAB=0, R/W=Read)

(Z180

MPU Write Only, Address XXF0H)

Receive Buffer Register

When the Z180 has assembled a byte of data to pass to the

PC/XT/AT, it places it in the Receive Buffer Register. If the

Received Data Available interrupt is enabled then an

interrupt is generated for the PC/XT/AT and the Data Ready

bit is set (if the Receive Timer is enabled, the interrupt and

setting of the Data Ready bit is delayed until after the timer

times out). Also the shadowed bits of the Line Status

Register are transferred to their respective bits when the

Z180 MPU writes to the Receive Buffer Register (See Line

Status Register Bits 1, 2, 3 and 4). This allows a simultaneous

setting of error bits when the data is written to the Receive

Buffer Register. In FIFO, mode this address is used to read

(PC) and write (Z180) the Receive FIFO.

0

0

0

0

0

0

0

0

D7

D6

D5

D4

D3

D2

D1

D0

Transmitter Holding Register

Figure 70. Transmit Holding Register

(PC Write Only, Address 00H, DLAB=0, R/W=Write)

(Z180 MPU Read Only, Address xxF0H)

Transmit Holding Register

When the PC/XT/AT writes to the Transmit Holding Register,

the Z80182/Z8L182 responds by setting the appropriate

bit in the IP register and by generating an interrupt to the

Z180 MPU if it is enabled. When the Z180 MPU reads this

register the Transmit Holding Register empty flag is set (if

the transmitter timer is enabled , this bit is set after the timer

times out). In FIFO mode of operation, this address is used

to read (Z180) and write (PC) the Transmitter FIFO.

0

0

0

0

0

0

0

0

D7

D6

D5

D4

D3

D2

D1

D0

DMA Mode Select

Reserved (Tx Overrun, MPU only)

Reserved (FCR Write, MPU only)

RCVR Trigger (LSB)

RCVR Trigger (MSB)

XMIT FIFO Reset

RCVR FIFO Reset

FIFO Enable

Figure 71. FIFO Control Register

(PC Write Only, Address 02H)

(Z180 MPU Read Only, Address xxE9H)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| Z8018533FSC | SMART PERIPHERAL CONTROLLERS |

| Z8019533FSC | SMART PERIPHERAL CONTROLLERS |

| Z80185 | SMART PERIPHERAL CONTROLLERS |

| Z8018520FSC | SMART PERIPHERAL CONTROLLERS |

| Z80195 | SMART PERIPHERAL CONTROLLERS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| Z80L18320ASC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

| Z80L183AZ033SCRXXXX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

| Z80PIO | 制造商:Zilog Inc 功能描述: |

| Z80S183 | 制造商:ZILOG 制造商全稱:ZILOG 功能描述:Family MPU |

| Z80S18333ASC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microprocessor |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。