- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373785 > ZL50018 (Zarlink Semiconductor Inc.) 2 K Digital Switch with Enhanced Stratum 3 DPLL PDF資料下載

參數(shù)資料

| 型號(hào): | ZL50018 |

| 廠商: | Zarlink Semiconductor Inc. |

| 英文描述: | 2 K Digital Switch with Enhanced Stratum 3 DPLL |

| 中文描述: | 2度數(shù)字交換機(jī)增強(qiáng)地層3數(shù)字鎖相環(huán) |

| 文件頁數(shù): | 74/136頁 |

| 文件大?。?/td> | 1448K |

| 代理商: | ZL50018 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁當(dāng)前第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁

ZL50018

Data Sheet

74

Zarlink Semiconductor Inc.

7 - 4

FFL3 - 0

Fast Frequency Lock Bits:

When the BLM bit in this register is high or when SM_FST

bit in the DPLLCR register is high, value of these bits (unsigned) represents fast locking

speed of the DPLL output clocks to the active input reference. The value also represents

speed grade that internal frequency value, used in holdover mode, reaches the DPLL

output frequency. The bigger the value, the faster the locking.

When both the BLM and the SM_FST bits are low, these bits are ignored.

3 - 0

LPF3 - 0

Low Pass Filter Control Bits:

Define the DPLL low pass filter corner frequency.

Note 1:

The default corner frequency (-3 dB point) of the low pass filter is 1.9 Hz.

Note 2:

To set fast lock mode, it is recommended to program the register bits as follows:

LPF3-0 ->’h8, unless a specific filter response (low pass filter characteristic) is required

FFL3-0 ->’hF

FLC3-0 ->’hF, if significant amount of jitter is not present on the active reference input

FLF_QS -> 1

BLM -> 1

Note 3:

In fast lock mode, it is important that the device is not also in freerun mode (see the RCCR Register). Otherwise, the

output frame pulse may not be generated correctly.

Note 4:

If the selected reference is 8 kHz, LPF3 - 0 should not be chosen to have corner frequency higher than 1/10 of the carrier

frequency, or 800Hz (i.e. bits LPF3 - 0 should have a value equal to or smaller than 1010).

Note 5:

When the FFL3 - 0 bits are used in normal locking mode (when the BLM bit is not set and the SM_FST bit in the DPLLCR

register is set), the DPLL locking time increases as the unsigned binary representation of FFL3 - 0 value increases,

maintaining given phase alignment speed (phase slope). The DPLL peaking, which is limited by some standards,

increases as well, so the FFL3 - 0 must be chosen with respect to given standard requirements.

Bit

Name

Description

Table 39 - Bandwidth Control Register (BWCR) Bits (continued)

External Read/Write Address: 004A

H

Reset Value: 0002

H

(see Note)

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0

0

BLM

FLF_

QS

FLC

3

FLC

2

FLC

1

FLC

0

FFL

3

FFL

2

FFL

1

FFL

0

LPF

3

LPF

2

LPF

1

LPF

0

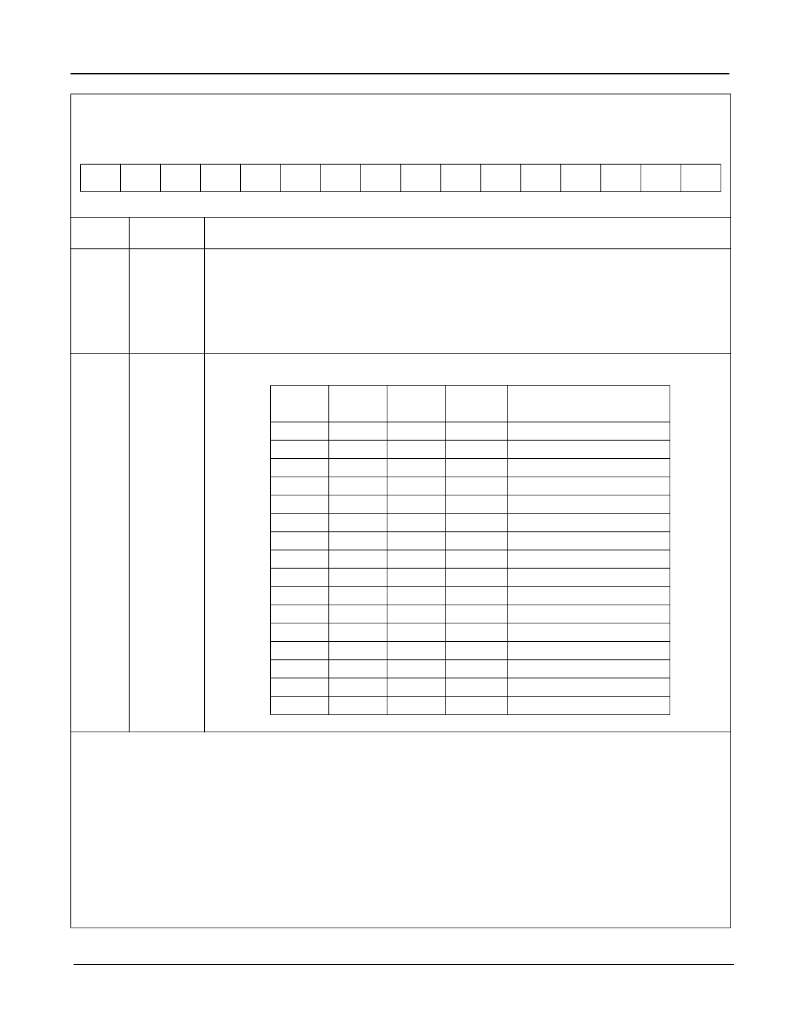

LPF3

LPF2

LPF1

LPF0

CORNER FREQUENCY OF

DPLL FILTER

0

0

0

0

0.47 Hz

0

0

0

1

0.95 Hz

0

0

1

0

1.9 Hz

0

0

1

1

3.8 Hz

0

1

0

0

7.6 Hz

0

1

0

1

15.2 Hz

0

1

1

0

30.4 Hz

0

1

1

1

60.7 Hz

1

0

0

0

121 Hz

1

0

0

1

243 Hz

1

0

1

0

486 Hz

1

0

1

1

971 Hz

1

1

0

0

1.94 kHz

1

1

0

1

3.88 kHz

1

1

1

0

7.77 kHz

1

1

1

1

15.54 kHz

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZL50018GAC | 2 K Digital Switch with Enhanced Stratum 3 DPLL |

| ZL50018QCC | 2 K Digital Switch with Enhanced Stratum 3 DPLL |

| ZL50019 | Enhanced 2 K Digital Switch with Stratum 4E DPLL |

| ZL50019GAC | Enhanced 2 K Digital Switch with Stratum 4E DPLL |

| ZL50019QCC | Enhanced 2 K Digital Switch with Stratum 4E DPLL |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ZL50018_06 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:2 K Digital Switch with Enhanced Stratum 3 DPLL |

| ZL50018GAC | 制造商:Microsemi Corporation 功能描述:SWIT FABRIC 2K X 2K 1.8V/3.3V 256BGA - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC TDM SWITCH 2K-CH ENH 256PBGA 制造商:Microsemi Corporation 功能描述:IC TDM SWITCH 2K-CH ENH 256PBGA |

| ZL50018GAG2 | 制造商:Microsemi Corporation 功能描述:SWIT FABRIC 2K X 2K 1.8V/3.3V 256BGA - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC TDM SWITCH 2K-CH ENH 256PBGA 制造商:Microsemi Corporation 功能描述:IC TDM SWITCH 2K-CH ENH 256PBGA |

| ZL50018QCC | 制造商:Microsemi Corporation 功能描述:SWIT FABRIC 2K X 2K 1.8V/3.3V 256LQFP - Trays |

| ZL50018QCG1 | 制造商:Microsemi Corporation 功能描述:PB FREE 2K+ RATE CONVERSION AND S3 DPLL - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC TDM SWITCH 2K-CH ENH 256LQFP |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。