- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄293745 > 1893YI-10 (INTEGRATED DEVICE TECHNOLOGY INC) DATACOM, INTERFACE CIRCUIT, PQFP64 PDF資料下載

參數(shù)資料

| 型號: | 1893YI-10 |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 網(wǎng)絡(luò)接口 |

| 英文描述: | DATACOM, INTERFACE CIRCUIT, PQFP64 |

| 封裝: | 10 X 10 MM, TQFP-64 |

| 文件頁數(shù): | 17/152頁 |

| 文件大小: | 943K |

| 代理商: | 1893YI-10 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當(dāng)前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁

Chapter 9

Pin Diagram, Listings, and Descriptions

ICS1893 Rev C 6/6/00

June, 2000

113

ICS1893 - Release

Copyright 2000, Integrated Circuit Systems, Inc.

All rights reserved.

MDIO

30

Input/

Output

Management Data Input/Output.

The signal on this pin can be tri-stated and can be driven by one of the

following:

A Station Management Entity (STA), to transfer command and data

information to the registers of the ICS1893.

The ICS1893, to transfer status information.

All transfers and sampling are synchronous with the signal on the MDC

pin.

Note: If the ICS1893 is to be used in an application that uses the

mechanical MII specification, MDIO must have a 1.5 k

±5%

pull-up resistor at the ICS1893 end and a 2 k

±5% pull-down

resistor at the station management end. (These resistors enable

the station management to determine if the connection is intact.)

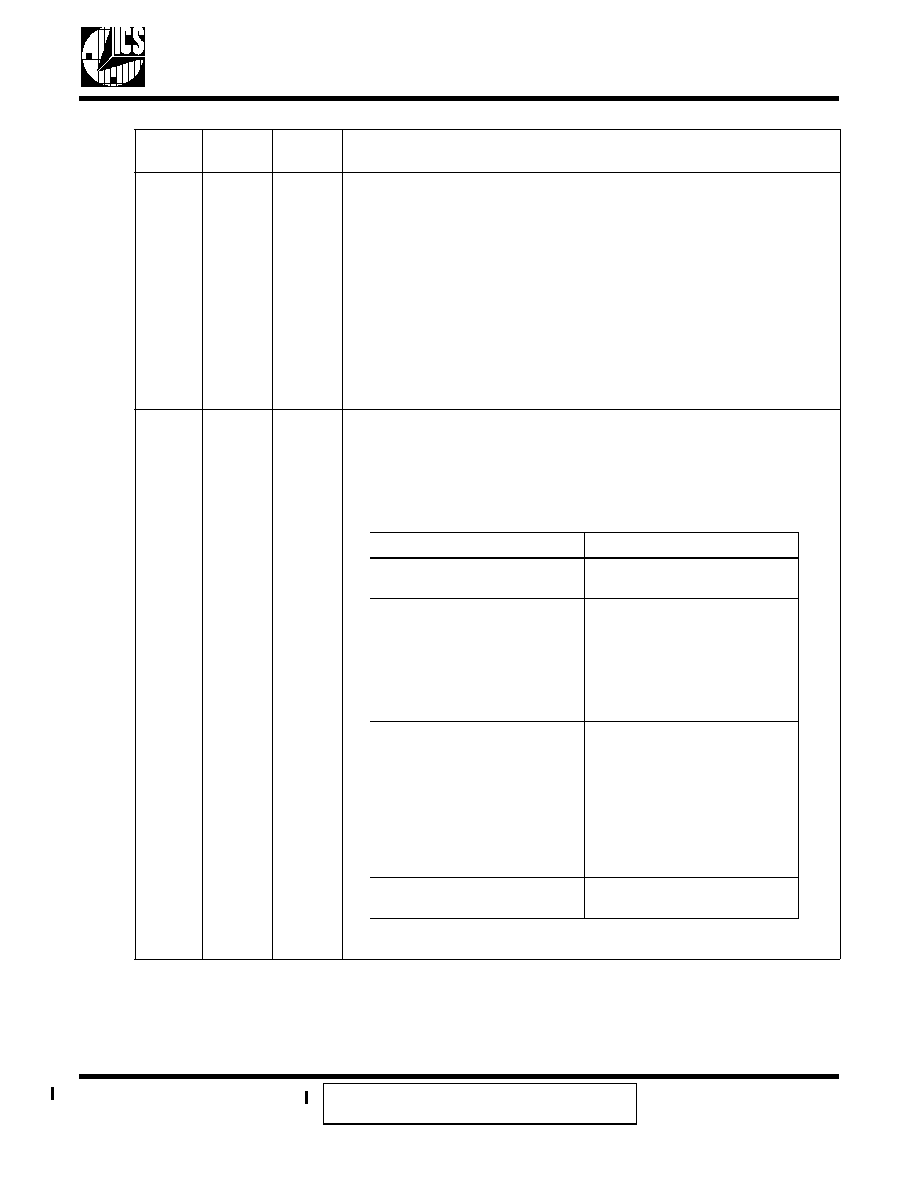

RXCLK

38

Output

Receive Clock.

The ICS1893 sources the RXCLK to the MAC/repeater interface. The

ICS1893 uses RXCLK to synchronize the signals on the following pins:

RXD[3:0], RXDV, and RXER. The following table contrasts the behavior

on the RXCLK pin when the mode for the ICS1893 is either 10Base-T or

100Base-TX.

Note: The signal on the RXCLK pin is conditioned by the RXTRI pin.

Table 9-5.

MAC/Repeater Interface Pins: Media Independent Interface (MII) (Continued)

Pin

Name

Pin

Number

Pin

Type

Pin Description

10Base-T

100Base-TX

The RXCLK frequency is 2.5

MHz.

The RXCLK frequency is 25 MHz.

The ICS1893 generates its

RXCLK from the MDI data stream

using a digital PLL. When the MDI

data stream terminates, the PLL

continues to operate,

synchronously referenced to the

last packet received.

The ICS1893 generates its

RXCLK from the MDI data stream

while there is a valid link (that is,

either data or IDLEs). In the

absence of a link, the ICS1893

uses the REF_IN clock to

generate the RXCLK.

The ICS1893 switches between

clock sources during the period

between when its CRS is

asserted and prior to its RXDV

being asserted. While the

ICS1893 is locking onto the

incoming data stream, a clock

phase change of up to 360

degrees can occur.

While the ICS1893 is bringing up

a link, a clock phase change of up

to 360 degrees can occur.

The RXCLK aligns once per

packet.

The RXCLK aligns once, when

the link is being established.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 1894-40KLF | DATACOM, INTERFACE CIRCUIT, QCC40 |

| 1894-40KLFT | DATACOM, INTERFACE CIRCUIT, QCC40 |

| 1895230000 | 15 A, STRIP TERMINAL BLOCK, 2 ROWS, 2 DECKS |

| 18F-08P-241 | 8 CONTACT(S), CABLE MOUNT, MINI DIN CONNECTOR, PLUG |

| 18F-08P-244 | 8 CONTACT(S), CABLE MOUNT, MINI DIN CONNECTOR, PLUG |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 1893YI-10LF | 功能描述:以太網(wǎng) IC 3.3V 10/100 BASE TX INTEGRATED PHYCEIVER RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| 1893YI-10LFT | 功能描述:以太網(wǎng) IC 3.3V 10/100 BASE TX INTEGRATED PHYCEIVER RoHS:否 制造商:Micrel 產(chǎn)品:Ethernet Switches 收發(fā)器數(shù)量:2 數(shù)據(jù)速率:10 Mb/s, 100 Mb/s 電源電壓-最大:1.25 V, 3.45 V 電源電壓-最小:1.15 V, 3.15 V 最大工作溫度:+ 85 C 封裝 / 箱體:QFN-64 封裝:Tray |

| 1894 | 功能描述:支架與墊片 HEX .187X.625 ALUM RoHS:否 制造商:Schurter 類型:Transipillar Spacers 長度:16 m 螺紋大小:M4 外徑:10 mm 材料:Nylon with Steel 電鍍:Zinc |

| 1894# | 制造商:Fluke Electronics 功能描述:BNC (F)/BANANA PLUG 制造商:Pomona Electronics 功能描述: |

| 1894 | 制造商:Pomona Electronics 功能描述:ADAPTER BNC FEMALE-BANANA PLUG 制造商:Pomona Electronics 功能描述:ADAPTER, BNC FEMALE-BANANA PLUG |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。